83058

Overview

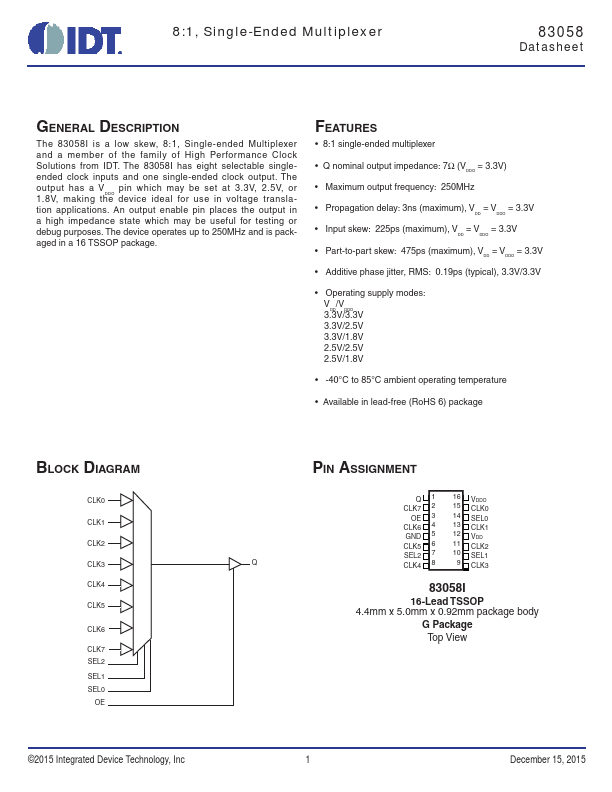

The 83058I is a low skew, 8:1, Single-ended Multiplexer and a member of the family of High Performance Clock Solutions from IDT. The 83058I has eight selectable singleended clock inputs and one single-ended clock output.

- 8:1 single-ended multiplexer

- Q nominal output impedance: 7Ω (V = 3.3V) DDO

- Maximum output frequency: 250MHz

- Propagation delay: 3ns (maximum), V = V = 3.3V DD DDO

- Input skew: 225ps (maximum), V = V = 3.3V DD DDO

- Part-to-part skew: 475ps (maximum), V = V = 3.3V DD DDO

- Additive phase jitter, RMS: 0.19ps (typical), 3.3V/3.3V

- Operating supply mod