8V19N408 Description

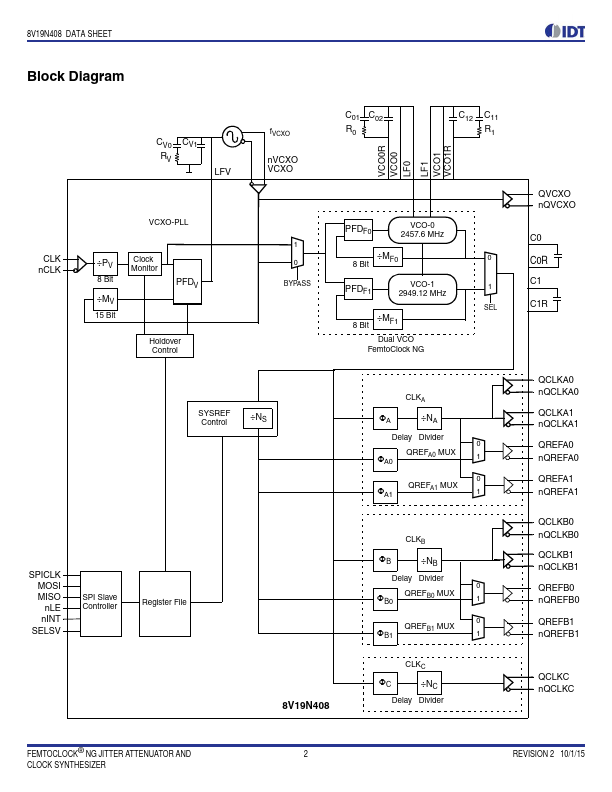

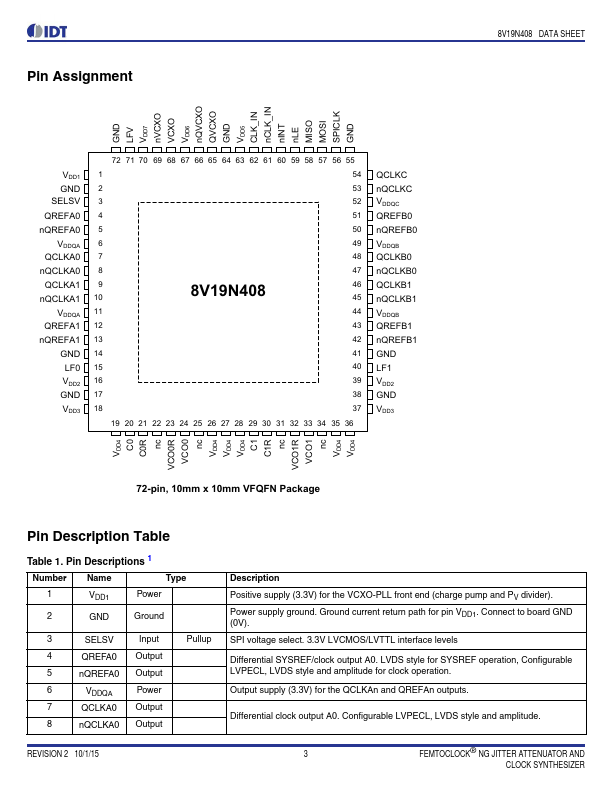

8V19N408 is a fully integrated FemtoClock® NG Jitter Attenuator and Clock Synthesizer. The device is a high-performance clock solution for conditioning and frequency/phase management of wireless base station radio equipment boards and is optimized to deliver excellent phase noise performance. The device supports JESD204B subclass 0 and 1 clock implementations.

8V19N408 Key Features

- Core timing unit for JESD204B wireless infrastructure clocks

- Fourth generation FemtoClock® NG technology

- First stage PLL uses an external VCXO for jitter attenuation

- Second PLL stage facilitates a dual integrated VCO for flexible

- Integrated VCO frequencies: 2400MHz

- 2500MHz (VCO-0) and

- 3000MHz (VCO-1)

- Five differential configurable LVPECL, LVDS clock outputs with a

- Four differential LVDS system reference (SYSREF) signal outputs

- Synchronization between clock and system reference signals