ICS571 Key Features

- Packaged in 8-pin SOIC (Pb free)

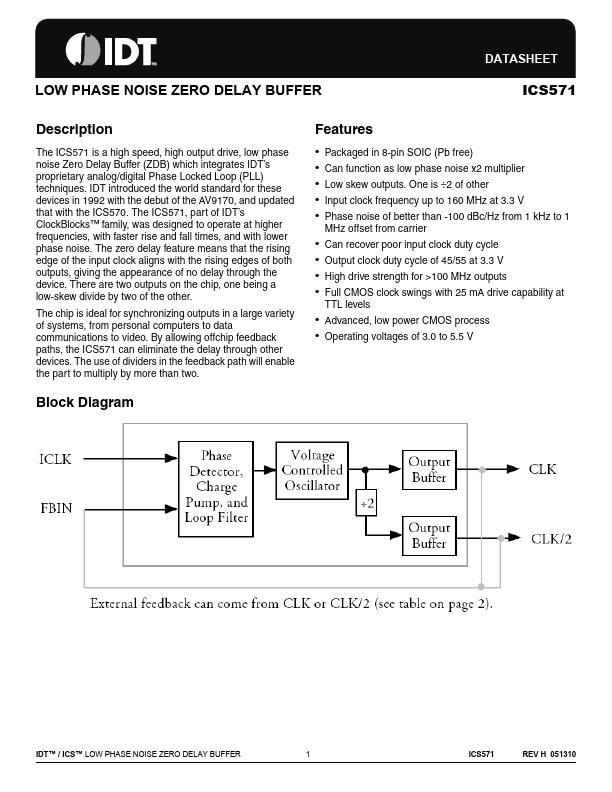

- Can function as low phase noise x2 multiplier

- Low skew outputs. One is ÷2 of other

- Input clock frequency up to 160 MHz at 3.3 V

- Phase noise of better than -100 dBc/Hz from 1 kHz to 1

- Can recover poor input clock duty cycle

- Output clock duty cycle of 45/55 at 3.3 V

- High drive strength for >100 MHz outputs

- Full CMOS clock swings with 25 mA drive capability at

- Advanced, low power CMOS process