Datasheet Summary

PLL BUILDING BLOCK

Description

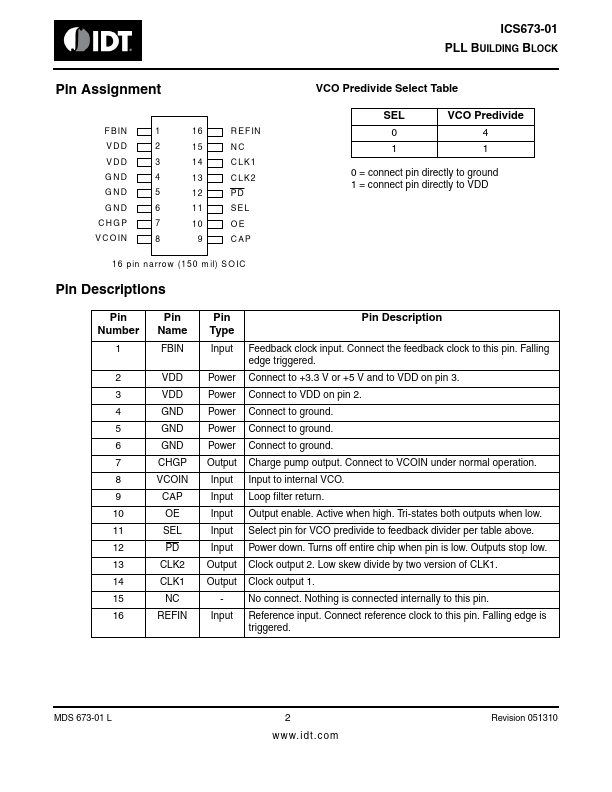

The ICS673-01 is a low cost, high performance Phase Locked Loop (PLL) designed for clock synthesis and synchronization. Included on the chip are the phase detector, charge pump, Voltage Controlled Oscillator (VCO), and two output buffers. One output buffer is a divide by two of the other. Through the use of external reference and VCO dividers (the ICS674-01), the user can customize the clock to lock to a wide variety of input frequencies.

The ICS673-01 also has an output enable function that puts both outputs into a high-impedance state. The chip also has a power down feature which turns off the entire device.

For applications that require low...