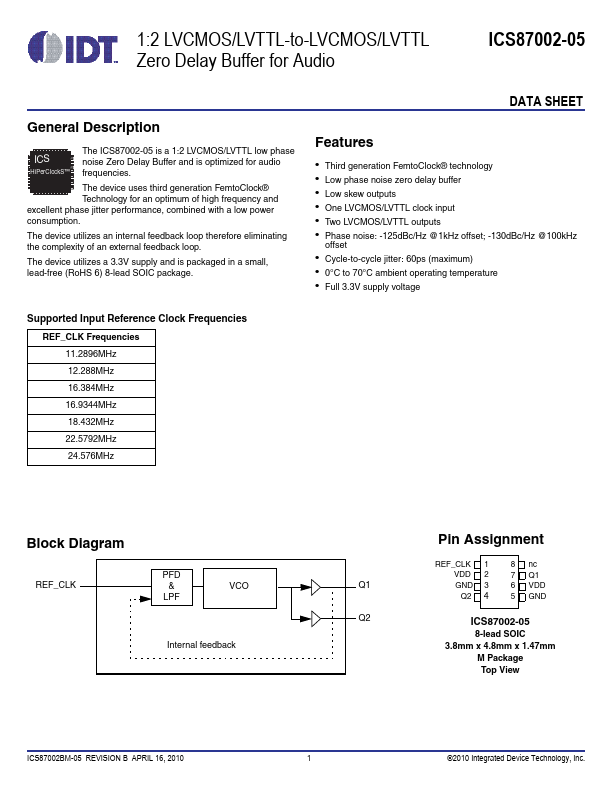

ICS87002-05 Key Features

- Third generation FemtoClock® technology

- Low phase noise zero delay buffer

- Low skew outputs

- One LVCMOS/LVTTL clock input

- Two LVCMOS/LVTTL outputs

- Phase noise: -125dBc/Hz @1kHz offset; -130dBc/Hz @100kHz

- Cycle-to-cycle jitter: 60ps (maximum)

- 0°C to 70°C ambient operating temperature

- Full 3.3V supply voltage