Datasheet Summary

LOW SKEW, 1-TO-8 DIFFERENTIAL-TO-LVCMOS/LVTTL CLOCK GENERATOR

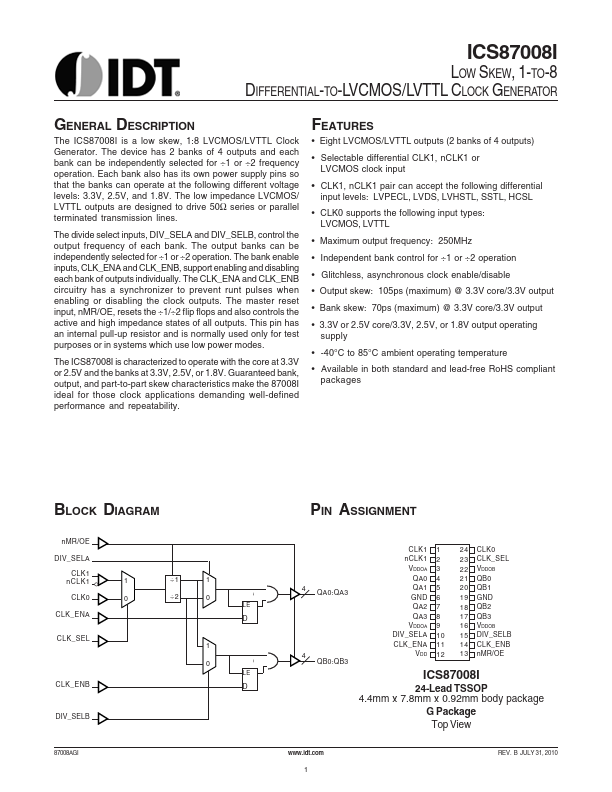

GENERAL DESCRIPTION

The ICS87008I is a low skew, 1:8 LVCMOS/LVTTL Clock Generator. The device has 2 banks of 4 outputs and each bank can be independently selected for ÷1 or ÷2 frequency operation. Each bank also has its own power supply pins so that the banks can operate at the following different voltage levels: 3.3V, 2.5V, and 1.8V. The low impedance LVCMOS/ LVTTL outputs are designed to drive 50Ω series or parallel terminated transmission lines.

The divide select inputs, DIV_SELA and DIV_SELB, control the output frequency of each bank. The output banks can be independently selected for ÷1 or ÷2 operation. The bank...