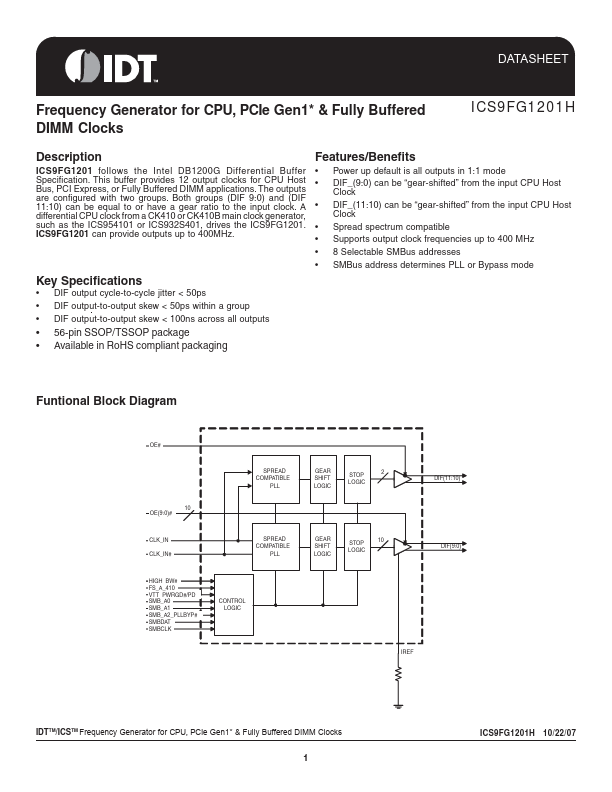

| Part | ICS9FG1201H |

|---|---|

| Description | Frequency Generator |

| Manufacturer | IDT |

| Size | 261.14 KB |

Pricing from 99.99 USD, available from Flip Electronics and Component Stockers USA.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Flip Electronics | 4506 | - | View Offer |

| Component Stockers USA | 641 | 1+ : 99.99 USD | View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| ICS9FG1201H | Renesas | Frequency Gearing Clock |