IDT70V631S

Overview

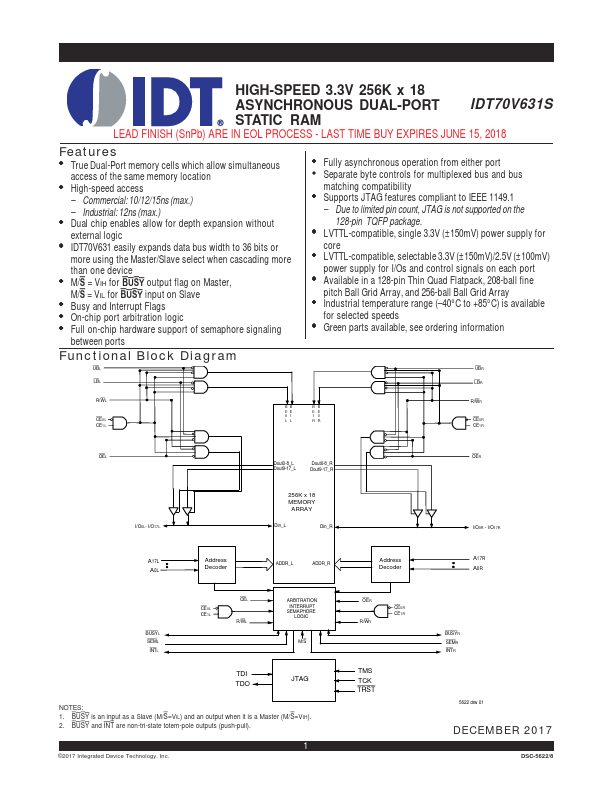

- Fully asynchronous operation from either port Separate byte controls for multiplexed bus and bus matching compatibility Supports JTAG features compliant to IEEE 1149.1 - Due to limited pin count, JTAG is not supported on the 128-pin TQFP package. LVTTL-compatible, single 3.3V (±150mV) power supply for core LVTTL-compatible, selectable 3.3V (±150mV)/2.5V (±100mV) power supply for I/Os and control signals on each port Available in a 128-pin Thin Quad Flatpack, 208-ball fine pitch Ball Grid Array, and 256-ball Ball Grid Array Industrial temperature range (-40°C to +85°C) is available for selected speeds Functional Block Diagram UBL LBL UBR LBR R/ WL