Datasheet Summary

..

ADVANCE INFORMATION

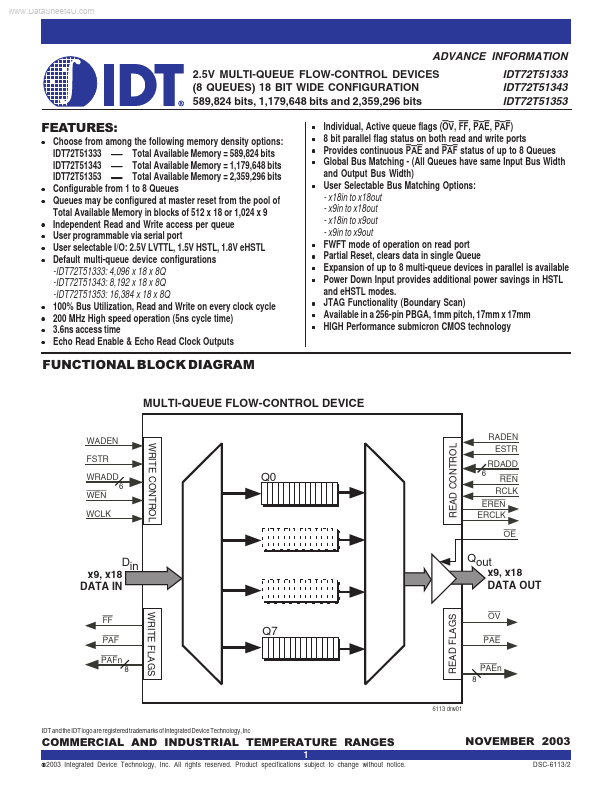

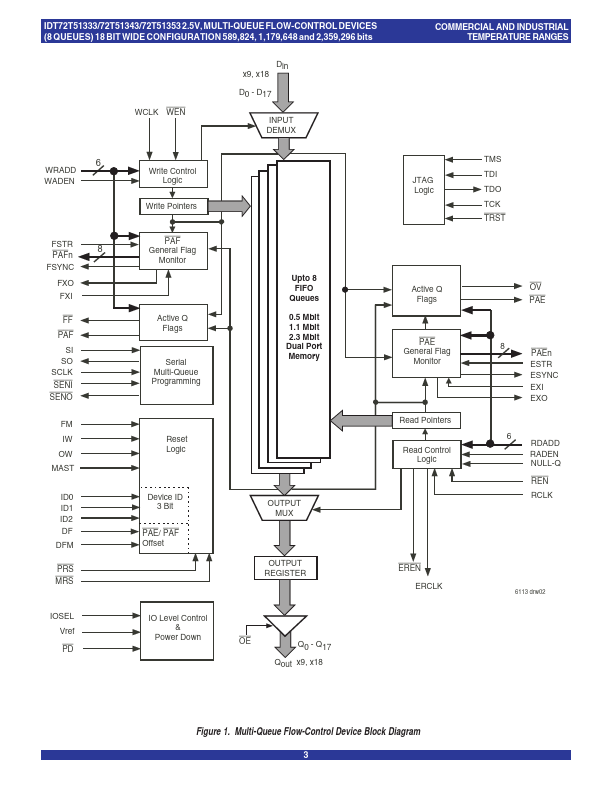

2.5V MULTI-QUEUE FLOW-CONTROL DEVICES (8 QUEUES) 18 BIT WIDE CONFIGURATION 589,824 bits, 1,179,648 bits and 2,359,296 bits

IDT72T51333 IDT72T51343 IDT72T51353

Features

:

- -

- -

- -

- -

- -

- Choose from among the following memory density options: IDT72T51333 Total Available Memory = 589,824 bits IDT72T51343 Total Available Memory = 1,179,648 bits IDT72T51353 Total Available Memory = 2,359,296 bits Configurable from 1 to 8 Queues Queues may be configured at master reset from the pool of Total Available Memory in blocks of 512 x 18 or 1,024 x 9 Independent Read and Write access per queue User programmable via serial port User selectable...