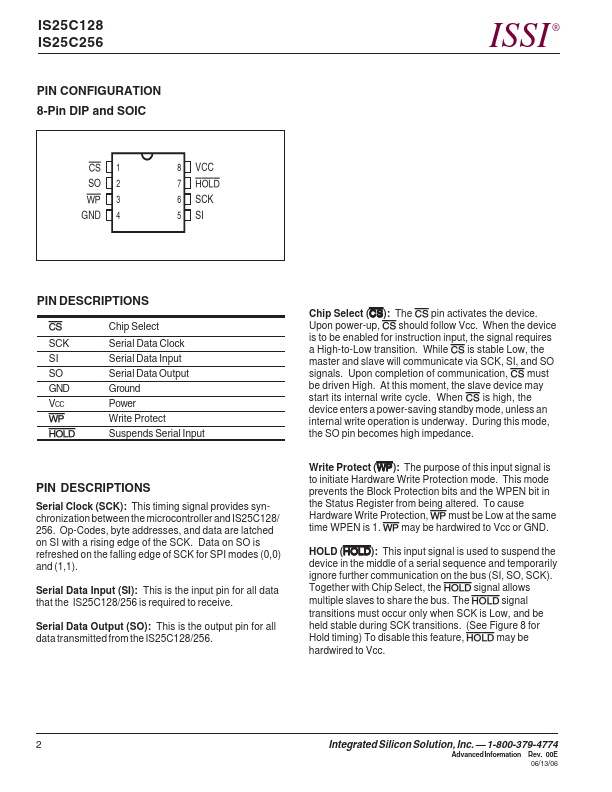

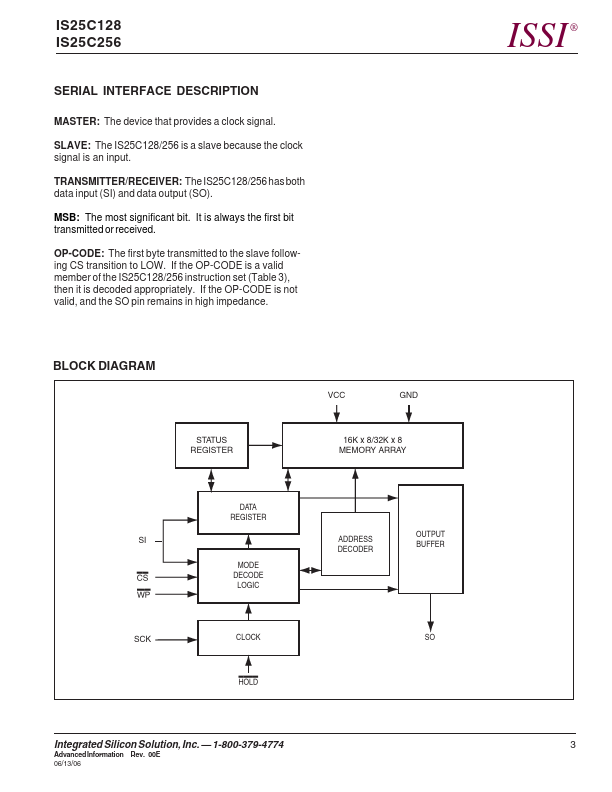

IS25C128 Description

The IS25C128 and IS25C256 are electrically erasable PROM devices that use the Serial Peripheral Interface (SPI) for munications. The IS25C128/256 EEPROMs are offered in a wide operating voltage range of 1.8V to 5.5V for patibility with most application voltages. ISSI designed the IS25C128/256 to be an efficient SPI EEPROM solution.

IS25C128 Key Features

- Serial Peripheral Interface (SPI) patible

- Supports SPI Modes 0 (0,0) and 3 (1,1)

- Low power CMOS

- Active current less than 3.0 mA (2.5V)

- Standby current less than 20 µA (2.5V)

- Low-voltage Operation

- Vcc = 1.8V to 5.5V

- Block Write Protection

- Protect 1/4, 1/2, or Entire Array

- 64 byte page write mode