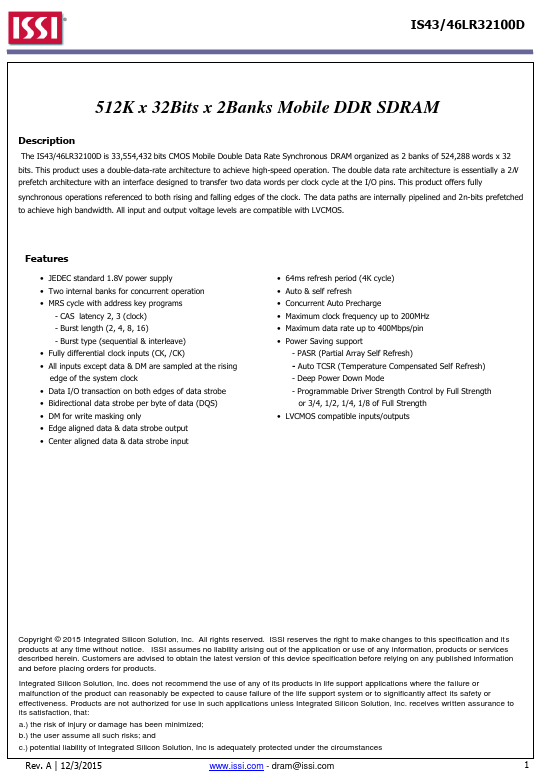

IS43LR32100D Overview

Description

The IS43/46LR32100D is 33,554,432 bits CMOS Mobile Double Data Rate Synchronous DRAM organized as 2 banks of 524,288 words x 32 bits. This product uses a double-data-rate architecture to achieve high-speed operation.

Key Features

- JEDEC standard 1.8V power supply

- Two internal banks for concurrent operation

- MRS cycle with address key programs

- CAS latency 2, 3 (clock)

- Burst length (2, 4, 8

- Burst type (sequential & interleave)

- Fully differential clock inputs (CK, /CK)

- All inputs except data & DM are sampled at the rising edge of the system clock

- Data I/O transaction on both edges of data strobe

- Bidirectional data strobe per byte of data (DQS)