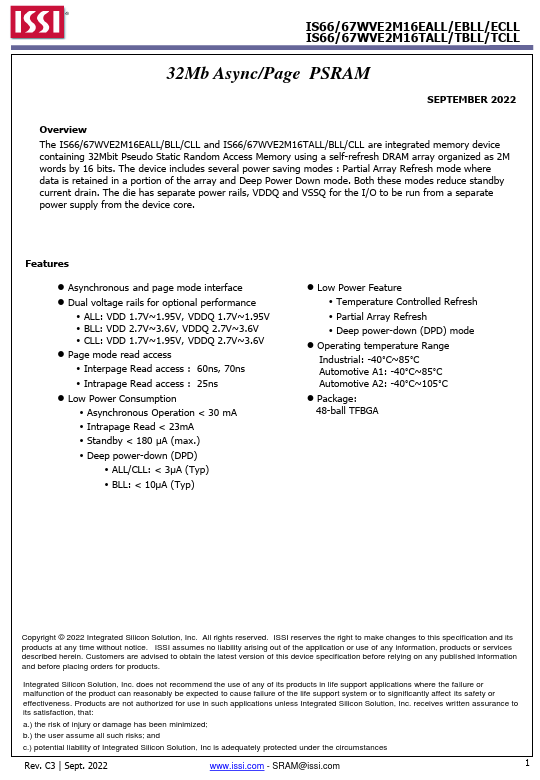

IS67WVE2M16TALL Overview

Key Specifications

Max Voltage (typical range): 1.95 V

Min Voltage (typical range): 1.7 V

Length: 8 mm

Width: 6 mm

Key Features

- Asynchronous and page mode interface

- Page mode read access Interpage Read access : 60ns, 70ns Intrapage Read access : 25ns

- Low Power Feature Temperature Controlled Refresh Partial Array Refresh Deep power-down (DPD) mode