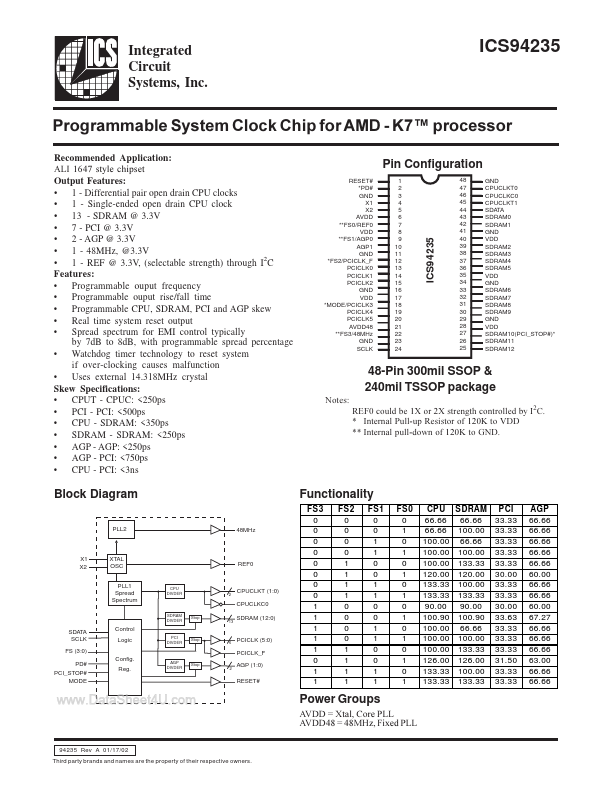

ICS94235 Overview

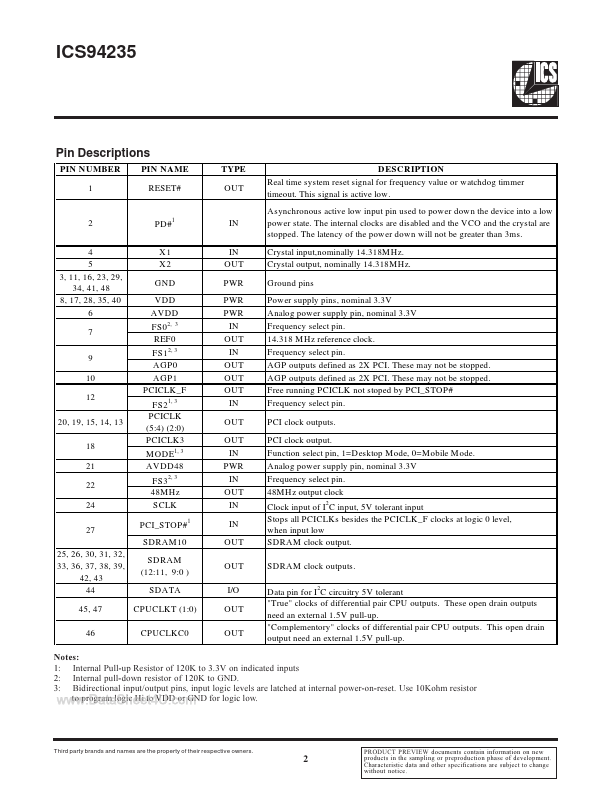

Real time system reset signal for frequency value or watchdog timmer timeout. This signal is active low. Asynchronous active low input pin used to power down the device into a low power state.

ICS94235 Key Features

- Differential pair open drain CPU clocks

- Single-ended open drain CPU clock

- SDRAM @ 3.3V

- PCI @ 3.3V

- AGP @ 3.3V

- 48MHz, @3.3V

- REF @ 3.3V, (selectable strength) through I2C Features

- Programmable ouput frequency

- Programmable ouput rise/fall time

- Programmable CPU, SDRAM, PCI and AGP skew