ICS507-xx Description

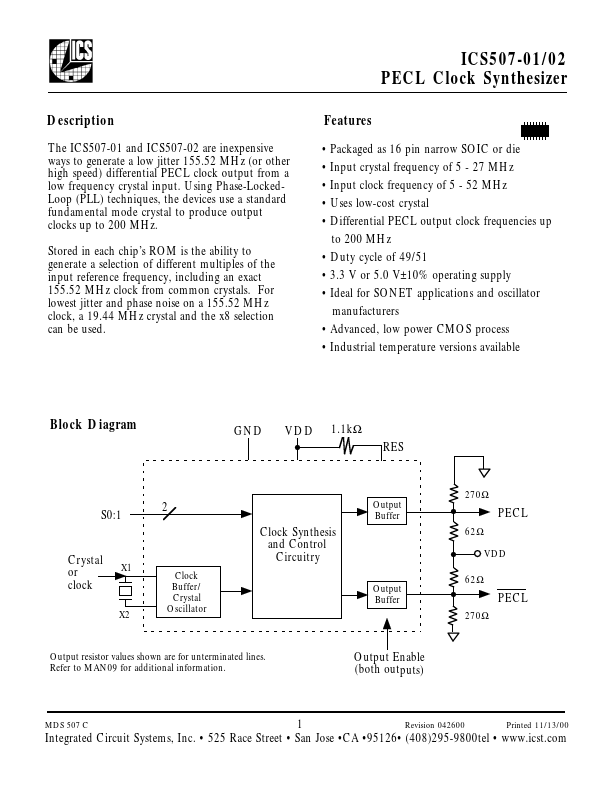

The ICS507-01 and ICS507-02 are inexpensive ways to generate a low jitter 155.52 MHz (or other high speed) differential PECL clock output from a low frequency crystal input. Using Phase-LockedLoop (PLL) techniques, the devices use a standard fundamental mode crystal to produce output clocks up to 200 MHz. Stored in each chip’s ROM is the ability to generate a selection of different multiples of the input reference...

ICS507-xx Key Features

- Packaged as 16 pin narrow SOIC or die

- Input crystal frequency of 5

- 27 MHz

- Input clock frequency of 5

- 52 MHz

- Uses low-cost crystal

- Differential PECL output clock frequencies up to 200 MHz

- Duty cycle of 49/51

- 3.3 V or 5.0 V±10% operating supply

- Ideal for SONET