ICS8624 Description

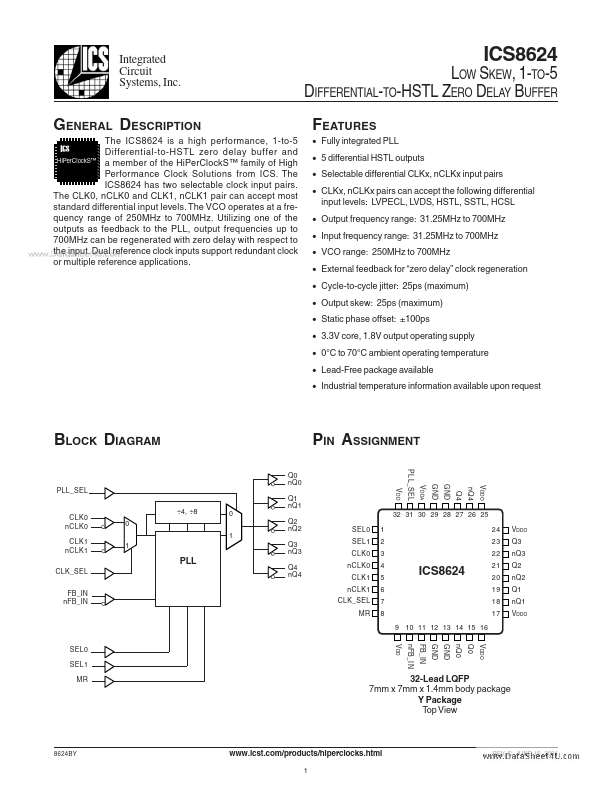

The ICS8624 is a high performance, 1-to-5 Differential-to-HSTL zero delay buffer and HiPerClockS™ a member of the HiPerClockS™ family of High Performance Clock Solutions from ICS. The ICS8624 has two selectable clock input pairs. The CLK0, nCLK0 and CLK1, nCLK1 pair can accept most standard differential input levels.

ICS8624 Key Features

- Fully integrated PLL

- 5 differential HSTL outputs

- Selectable differential CLKx, nCLKx input pairs

- CLKx, nCLKx pairs can accept the following differential input levels: LVPECL, LVDS, HSTL, SSTL, HCSL

- Output frequency range: 31.25MHz to 700MHz

- Input frequency range: 31.25MHz to 700MHz

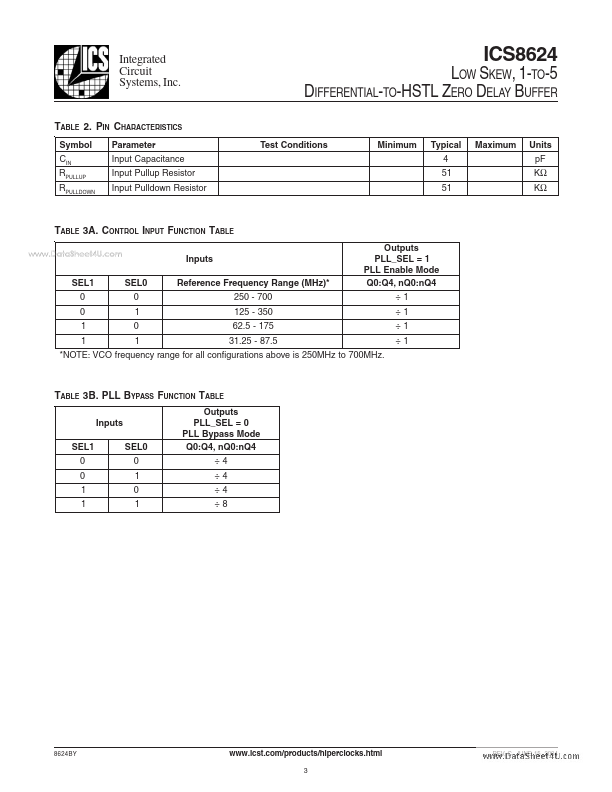

- VCO range: 250MHz to 700MHz

- External feedback for “zero delay” clock regeneration

- Cycle-to-cycle jitter: 25ps (maximum)

- Output skew: 25ps (maximum)