ICS95V857

ICS95V857 is 2.5V Wide Range Frequency Clock Driver manufactured by Integrated Circuit Systems.

Description

/Features

:

- Low skew, low jitter PLL clock driver

- 1 to 10 differential clock distribution (SSTL_2)

- Feedback pins for input to output synchronization

- PD# for power management

- Spread Spectrum-tolerant inputs

- Auto PD when input signal removed Specifications:

- Meets PC3200 Class A+ specification for DDR-I 400 support

- Covers all DDRI speed grades Switching Characteristics:

- CYCLE

- CYCLE jitter: <50ps

- OUTPUT

- OUTPUT skew: <40ps

- Period jitter: ±30ps

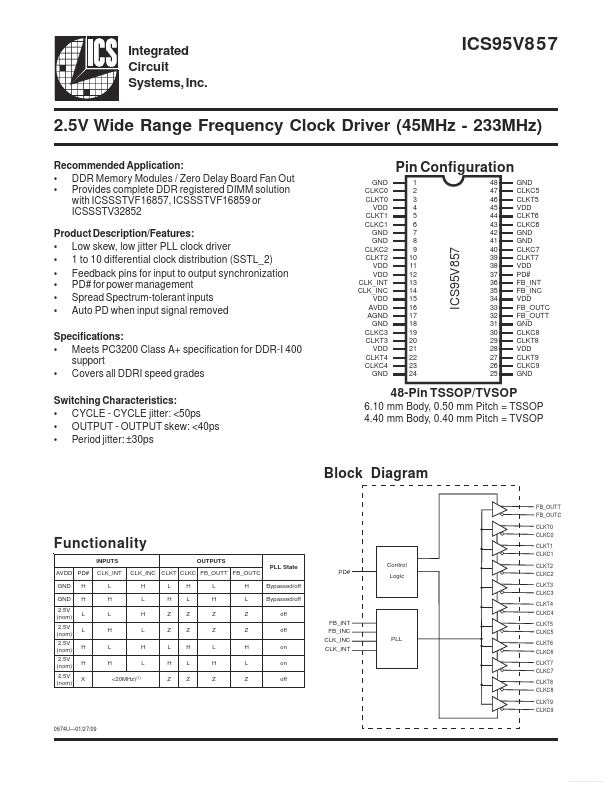

Pin Configuration

GND CLKC0 CLKT0 VDD CLKT1 CLKC1 GND GND CLKC2 CLKT2 VDD VDD CLK_INT CLK_INC VDD AVDD AGND GND CLKC3 CLKT3 VDD CLKT4 CLKC4 GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 GND CLKC5 CLKT5 VDD CLKT6 CLKC6 GND GND CLKC7 CLKT7 VDD PD# FB_INT FB_INC VDD FB_OUTC FB_OUTT GND CLKC8 CLKT8 VDD CLKT9 CLKC9 GND

48-Pin TSSOP/TVSOP

6.10 mm Body, 0.50 mm Pitch = TSSOP 4.40 mm Body, 0.40 mm Pitch = TVSOP

Block Diagram

FB_OUTT FB_OUTC CLKT0 CLKC0

Functionality

INPUTS AVDD PD# GND GND 2.5V (nom) 2.5V (nom) 2.5V (nom) 2.5V (nom) 2.5V (nom) H H L L H H X CLK_INT L H L H L H <20MHz)

(1)

CLKT1 CLKC1

OUTPUTS PLL State CLK_INC CLKT CLKC FB_OUTT FB_OUTC H L H L H L L H Z Z L H Z H L Z Z H L Z L H Z Z L H Z H L Z Z H L Z Bypassed/off Bypassed/off off off on on off

Control PD# Logic

CLKT2 CLKC2 CLKT3 CLKC3 CLKT4 CLKC4

FB_INT FB_INC CLK_INC CLK_INT

CLKT5 CLKC5

CLKT6 CLKC6 CLKT7 CLKC7 CLKT8 CLKC8 CLKT9 CLKC9

0674U- 01/27/09

Free Datasheet http://.n Datasheet.

Pin Configuration

1 A B C D E F G H J K 2 3 4 5 6

56-Ball BGA

Top View

A B C D E F G H J K 1 CLKT0 CLKC1 GND CLKT2 VDD CLK_INT VDD AGND CLKC3 CLKT4 2 CLKC0 CLKT1 GND CLKC2 VDD CLK_INC AVDD GND CLKT3 CLKC4 3 GND VDD NC NC NB NB NC NC VDD GND 4 GND VDD NC NC NB NB NC NC VDD GND 5 6 CLKC5 CLKT5 CLKT6 CLKC6 GND GND CLKC7 CLKT7 VDD PD# FB_INC FB_INT FB_OUTC VDD GND FB_OUTT CLKT8 CLKC8 CLKC9...