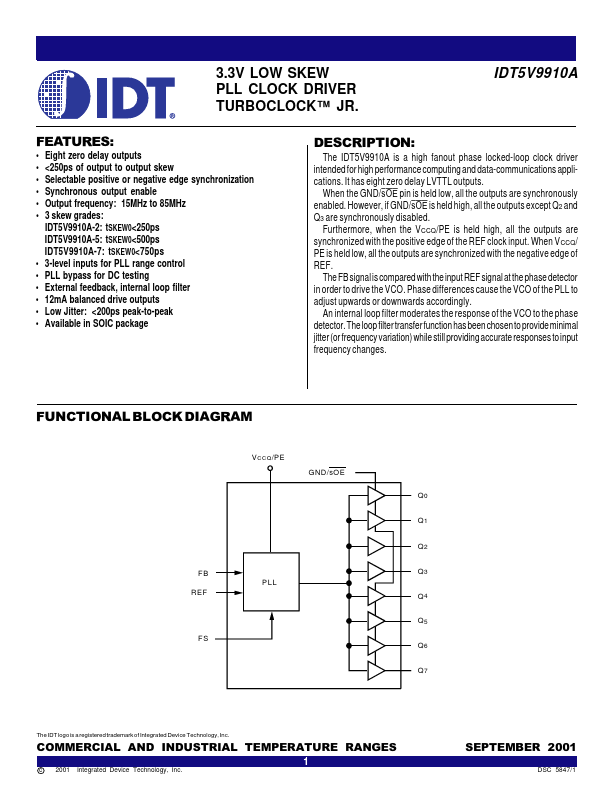

IDT5V9910A Overview

The IDT5V9910A is a high fanout phase locked-loop clock driver intended for high performance puting and data-munications applications. It has eight zero delay LVTTL outputs. When the GND/sOE pin is held low, all the outputs are synchronously enabled.

IDT5V9910A Key Features

- Eight zero delay outputs

- <250ps of output to output skew

- Selectable positive or negative edge synchronization

- Synchronous output enable

- Output frequency: 15MHz to 85MHz

- 3 skew grades

- 3-level inputs for PLL range control

- PLL bypass for DC testing

- External feedback, internal loop filter

- 12mA balanced drive outputs