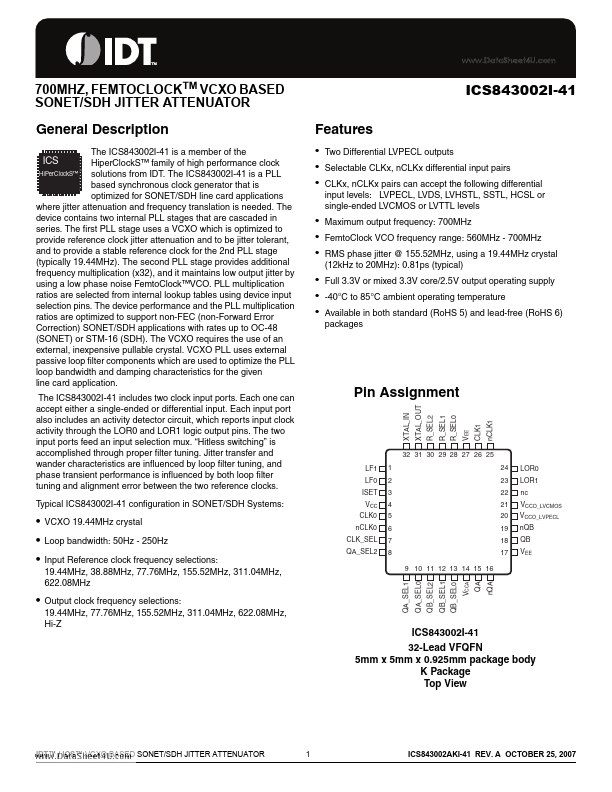

ICS843002I-41

ICS843002I-41 is 700MHZ FEMTOCLOCKTM VCXO BASED SONET/SDH JITTER ATTENUATOR manufactured by Integrated Device Technology.

Features

- -

- -

- -

- -

- Two Differential LVPECL outputs Selectable CLKx, n CLKx differential input pairs CLKx, n CLKx pairs can accept the following differential input levels: LVPECL, LVDS, LVHSTL, SSTL, HCSL or single-ended LVCMOS or LVTTL levels Maximum output frequency: 700MHz Femto Clock VCO frequency range: 560MHz

- 700MHz RMS phase jitter @ 155.52MHz, using a 19.44MHz crystal (12k Hz to 20MHz): 0.81ps (typical) Full 3.3V or mixed 3.3V core/2.5V output operating supply -40°C to 85°C ambient operating temperature Available in both standard (Ro HS 5) and lead-free (Ro HS 6) packages

General Description

The ICS843002I-41 is a member of the Hiper Clock S™ family of high performance clock Hi Per Clock S™ solutions from IDT. The ICS843002I-41 is a PLL based synchronous clock generator that is optimized for SONET/SDH line card applications where jitter attenuation and frequency translation is needed. The device contains two internal PLL stages that are cascaded in series. The first PLL stage uses a VCXO which is optimized to provide reference clock jitter attenuation and to be jitter tolerant, and to provide a stable reference clock for the 2nd PLL stage (typically 19.44MHz). The second PLL stage provides additional frequency multiplication (x32), and it maintains low output jitter by using a low phase noise Femto Clock™VCO. PLL multiplication ratios are selected from internal lookup tables using device input selection pins. The device performance and the PLL multiplication ratios are optimized to support non-FEC (non-Forward Error Correction) SONET/SDH applications with rates up to OC-48 (SONET) or STM-16 (SDH). The VCXO requires the use of an external, inexpensive pullable crystal. VCXO PLL uses external passive loop filter ponents which are used to optimize the PLL loop bandwidth and damping characteristics for the given line card application.

The ICS843002I-41 includes two clock input ports. Each one can accept either a single-ended or differential input. Each...