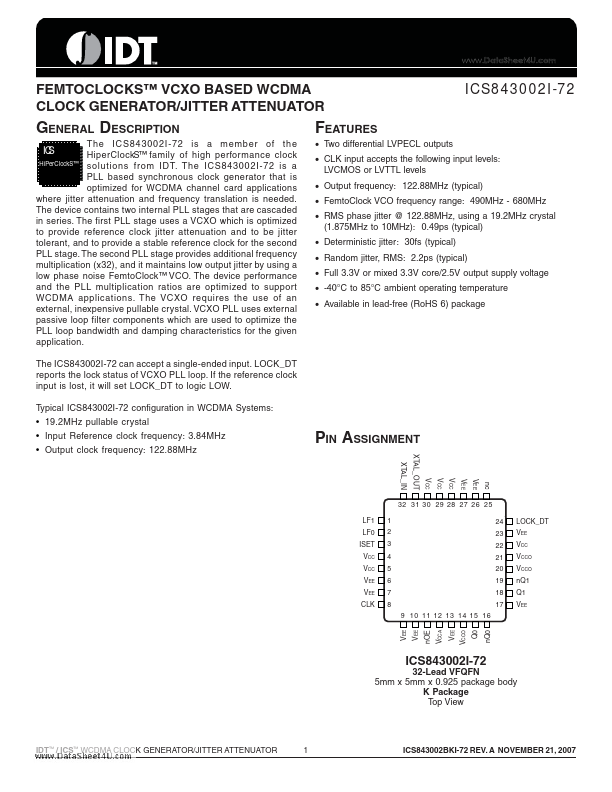

ICS843002I-72

ICS843002I-72 is FEMTOCLOCKS VCXO BASED WCDMA CLOCK GENERATOR/JITTER ATTENUATOR manufactured by Integrated Device Technology.

..

FEMTOCLOCKS™ VCXO BASED WCDMA CLOCK GENERATOR/JITTER ATTENUATOR

GENERAL DESCRIPTION

The ICS843002I-72 is a member of the IC S HiperClockS™ family of high performance clock HiPerClockS™ solutions from IDT. The ICS843002I-72 is a PLL based synchronous clock generator that is optimized for WCDMA channel card applications where jitter attenuation and frequency translation is needed. The device contains two internal PLL stages that are cascaded in series. The first PLL stage uses a VCXO which is optimized to provide reference clock jitter attenuation and to be jitter tolerant, and to provide a stable reference clock for the second PLL stage. The second PLL...