IDTCSPF2510C Description

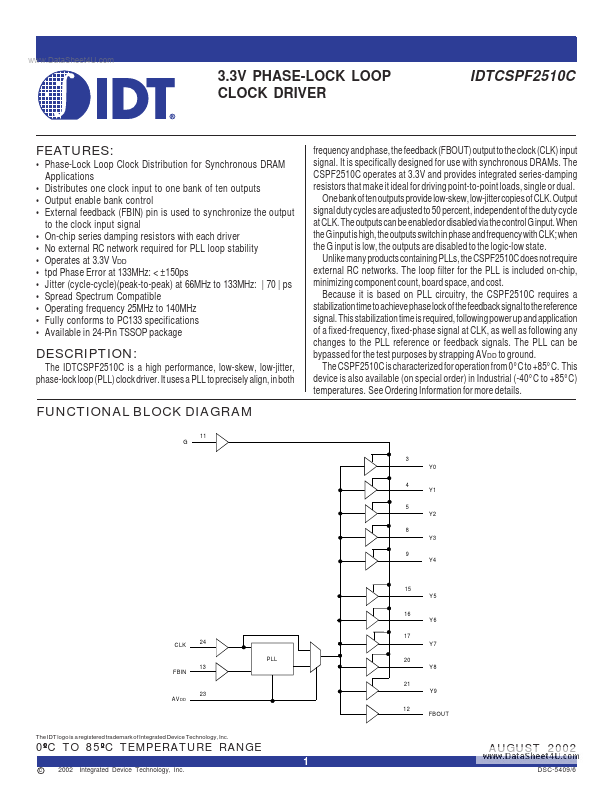

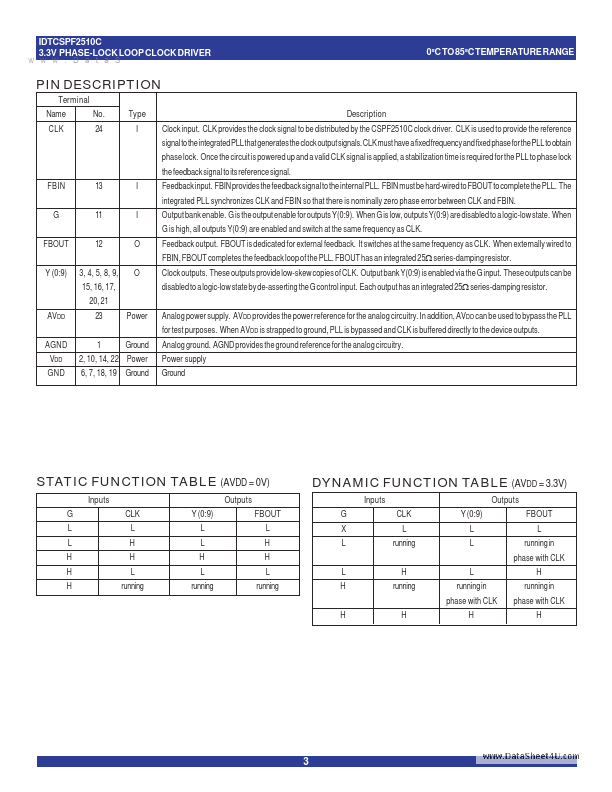

The IDTCSPF2510C is a high performance, low-skew, low-jitter, phase-lock loop (PLL) clock driver. It uses a PLL to precisely align, in both frequency and phase, the feedback (FBOUT) output to the clock (CLK) input signal. It is specifically designed for use with synchronous DRAMs.

IDTCSPF2510C Key Features

- Phase-Lock Loop Clock Distribution for Synchronous DRAM

IDTCSPF2510C Applications

- Distributes one clock input to one bank of ten outputs