IDTCSPT855

Overview

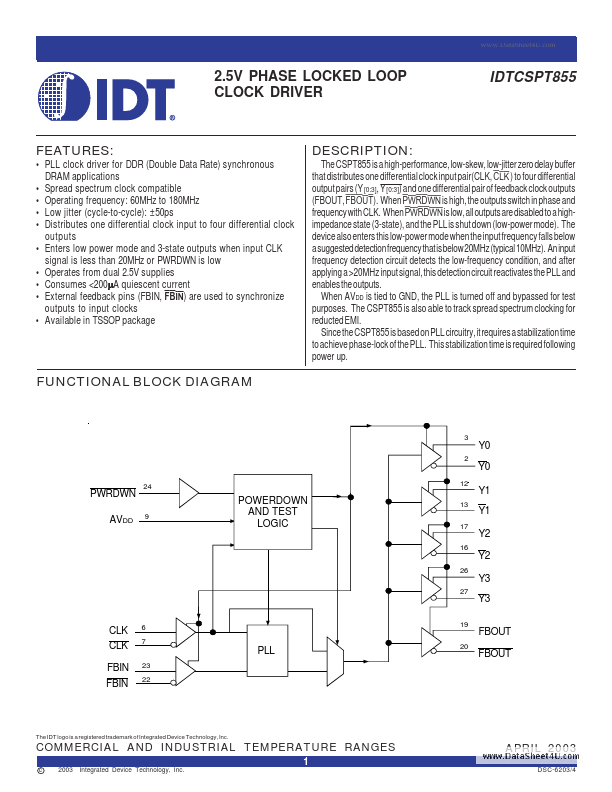

The CSPT855 is a high-performance, low-skew, low-jitter zero delay buffer that distributes one differential clock input pair(CLK, CLK ) to four differential output pairs (Y [0:3], Y [0:3]) and one differential pair of feedback clock outputs (FBOUT, FBOUT). When PWRDWN is high, the outputs switch in phase and frequency with CLK.