IDTCV119E Overview

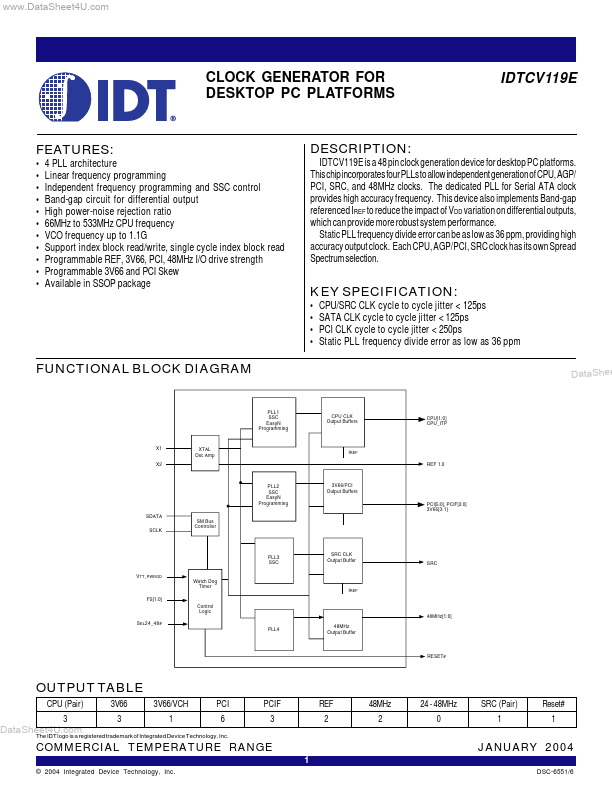

CPU/SRC CLK cycle to cycle jitter < 125ps SATA CLK cycle to cycle jitter < 125ps PCI CLK cycle to cycle jitter < 250ps Static PLL frequency divide error as low as 36 ppm FUNCTIONAL BLOCK DIAGRAM . The IDT logo is a registered trademark of Integrated Device Technology, Inc. MERCIAL TEMPERATURE RANGE 1 © 2004 Integrated Device Technology, Inc.

IDTCV119E Key Features

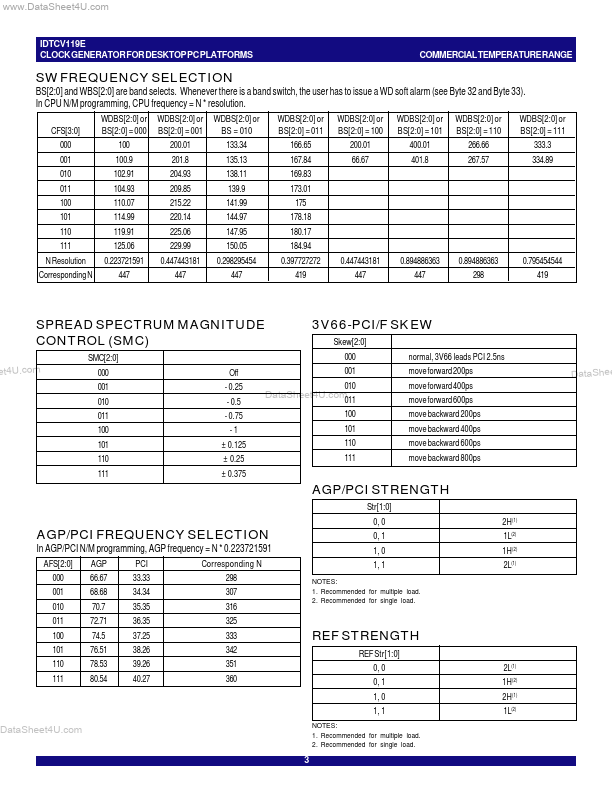

- 48MHz 0 SRC (Pair) 1 Reset# 1