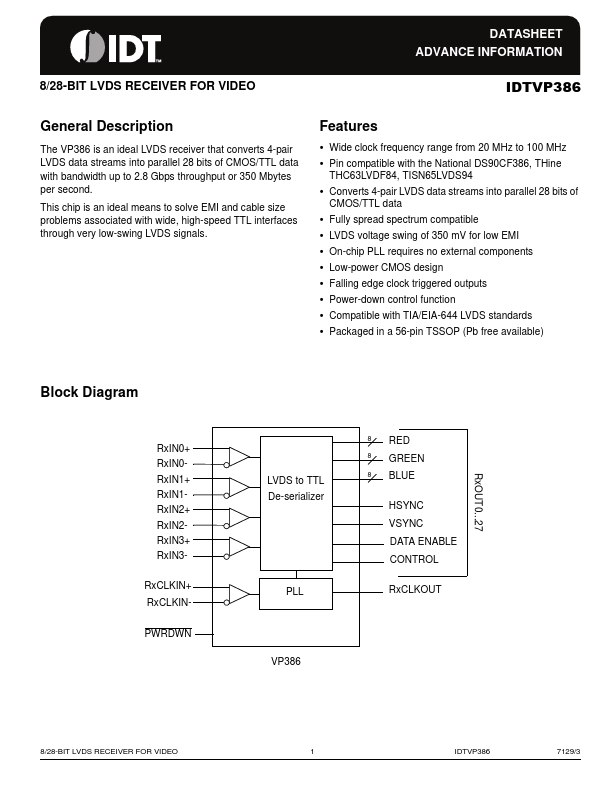

IDTVP386 Key Features

- Wide clock frequency range from 20 MHz to 100 MHz

- Pin patible with the National DS90CF386, THine

- Fully spread spectrum patible

- LVDS voltage swing of 350 mV for low EMI

- On-chip PLL requires no external ponents

- Low-power CMOS design

- Falling edge clock triggered outputs

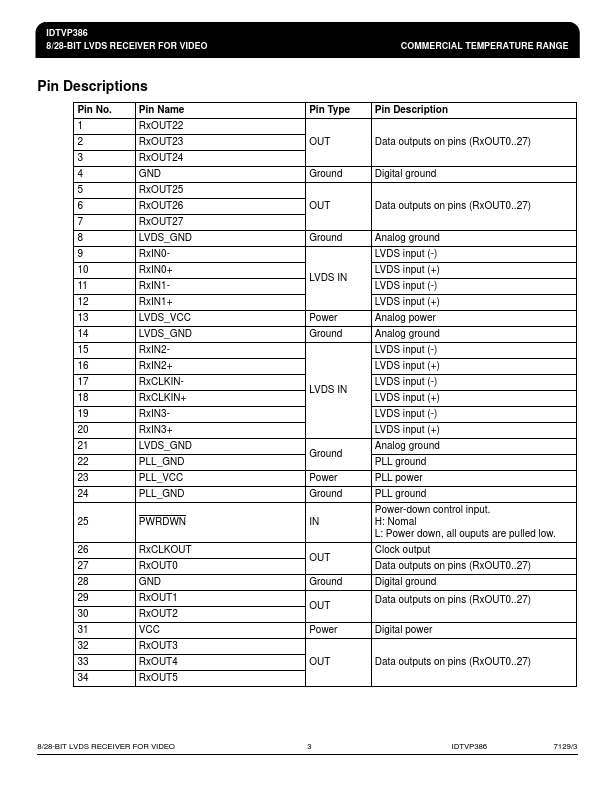

- Power-down control function

- patible with TIA/EIA-644 LVDS standards

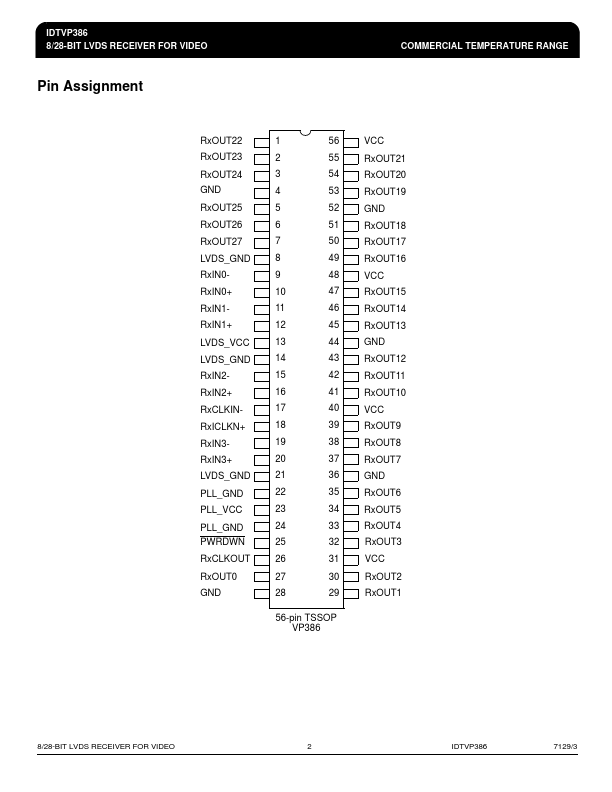

- Packaged in a 56-pin TSSOP (Pb free available)