| Part | IDT23S09E |

|---|---|

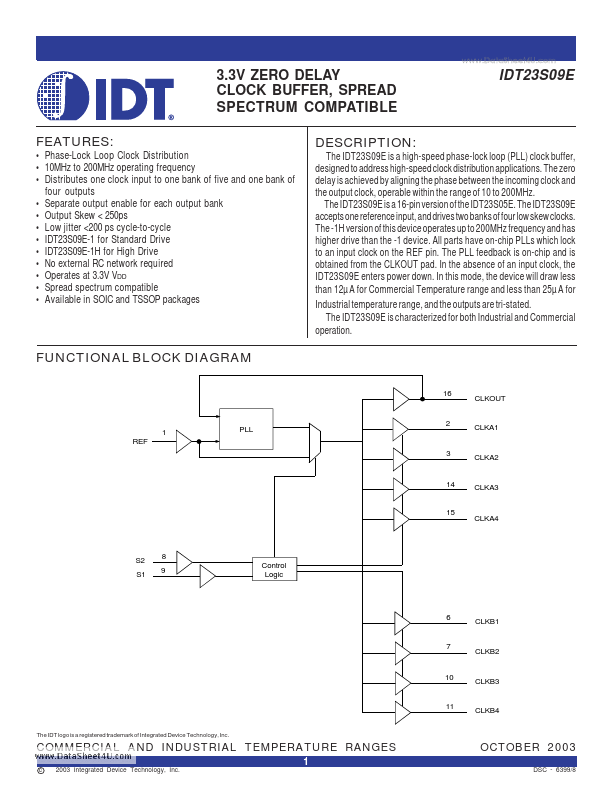

| Description | 3.3V ZERO DELAY CLOCK BUFFER |

| Manufacturer | Integrated Device Technology |

| Size | 83.64 KB |

Pricing from 99.99 USD, available from Component Stockers USA and Worldway Electronics.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Component Stockers USA | 507 | 1+ : 99.99 USD | View Offer |

| Worldway Electronics | 11580 | - | View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| IDT23S09E | Renesas | 3.3V ZERO DELAY CLOCK BUFFER |

| IDT23S09 | Integrated Device | IDT23S09 3.3V ZERO DELAY CLOCK BUFFER |

| IDT23S09 | Renesas | 3.3V ZERO DELAY CLOCK BUFFER |

| IDT23S05E | Integrated Device | 3.3V ZERO DELAY CLOCK BUFFER |

| IDT23S08T | Renesas | 2.5V ZERO DELAY CLOCK MULTIPLIER |