IS61NLF51236 Overview

Key Specifications

Package: LQFP

Pins: 100

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.465 V

Description

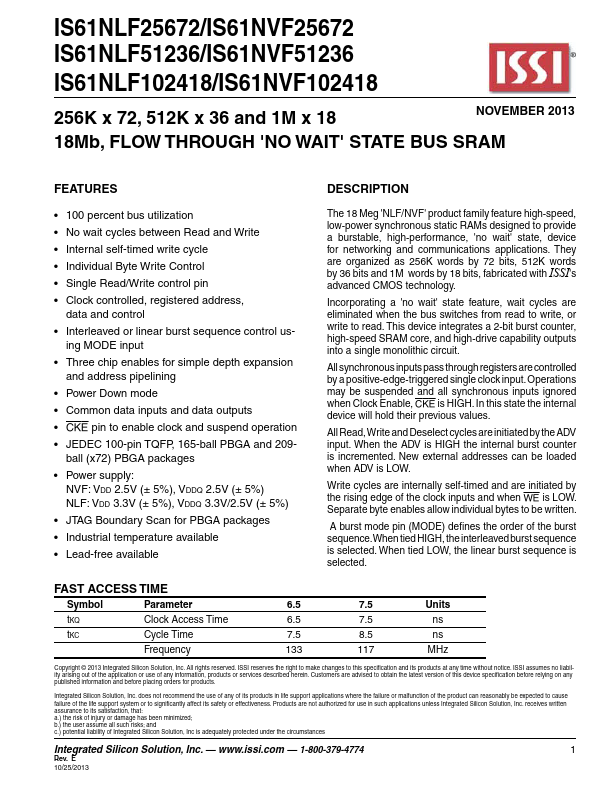

100 percent bus utilization - No wait cycles between Read and Write - Internal self-timed write cycle - Individual Byte Write Control - Single Read/Write control pin - Clock controlled, registered address, data and control - Interleaved or linear burst sequence control us- ing MODE input - Three chip enables for simple depth expansion and address pipelining - Power Down mode - Common data inputs and data outputs - CKE pin to enable clock and suspend operation - JEDEC 100-pin TQFP, 165-ball PBGA and 209- ball (x72) PBGA packages - Power supply: NVF: Vdd 2.5V (± 5%), Vddq 2.5V (± 5%) NLF: Vdd 3.3V (± 5%), Vddq 3.3V/2.5V (± 5%) - JTAG Boundary Scan for PBGA packages - Industrial temperature available - Lead-free available The 18 Meg 'NLF/NVF' product family feature high-speed, low-power synchronous static RAMs designed to provide a burstable, high-performance, 'no wait' state, device for networking and communications applications. They are organized as 256K words by 72 bits, 512K words by 36 bits and 1M words by 18 bits, fabricated with ISSI's advanced CMOS technology.