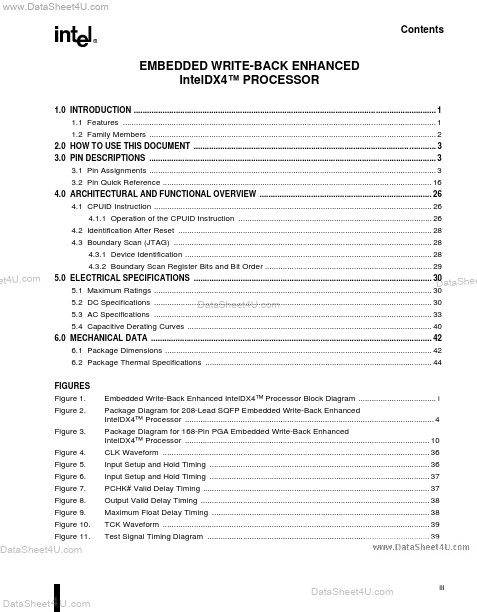

Datasheet Summary

..

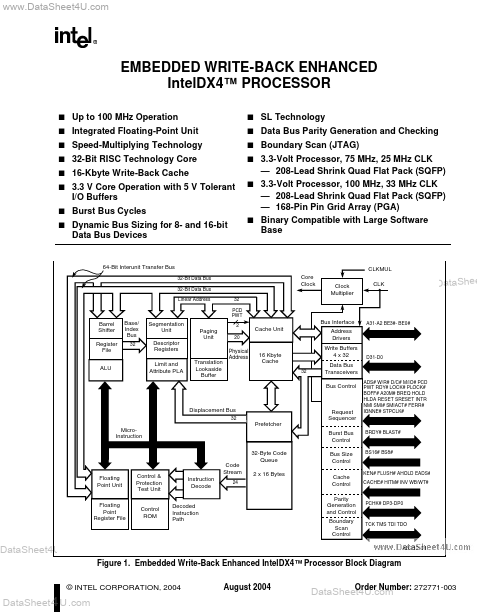

EMBEDDED WRITE-BACK ENHANCED IntelDX4™ PROCESSOR s Up to 100 MHz Operation s Integrated Floating-Point Unit s Speed-Multiplying Technology s 32-Bit RISC Technology Core s 16-Kbyte Write-Back Cache s 3.3 V Core Operation with 5 V Tolerant s SL Technology s Data Bus Parity Generation and Checking s Boundary Scan (JTAG) s 3.3-Volt Processor, 75 MHz, 25 MHz CLK

- 208-Lead Shrink Quad Flat Pack (SQFP) s 3.3-Volt Processor, 100 MHz, 33 MHz CLK

I/O Buffers s Burst Bus Cycles s Dynamic Bus Sizing for 8- and 16-bit

Data Bus Devices

- 208-Lead Shrink Quad Flat Pack (SQFP)

- 168-Pin Pin Grid Array (PGA) s Binary patible with Large Software Base

64-Bit Interunit Transfer...