RD38F4455LVY

Overview

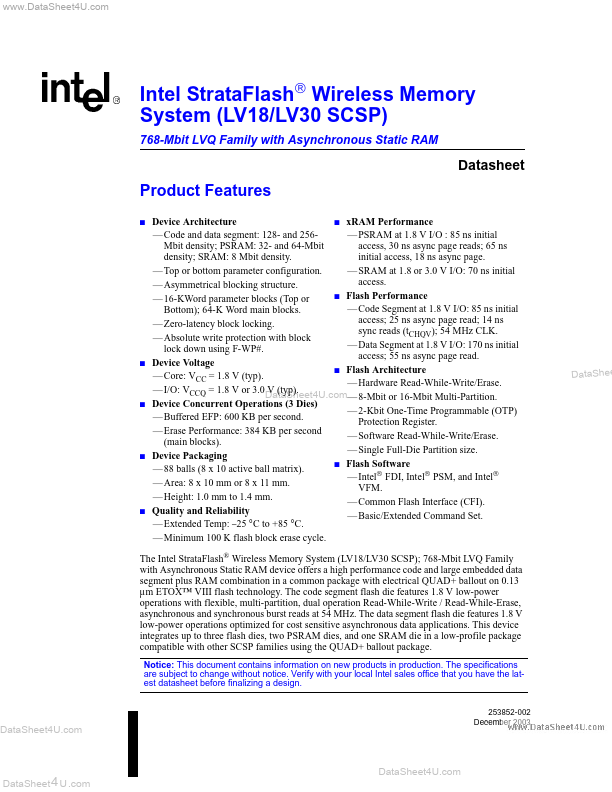

- Device Architecture

- xRAM Performance - Code and data segment: 128- and 256- PSRAM at 1.8 V I/O : 85 ns initial Mbit density; PSRAM: 32- and 64-Mbit access, 30 ns async page reads; 65 ns density; SRAM: 8 Mbit density. initial access, 18 ns async page. - Top or bottom parameter configuration. - SRAM at 1.8 or 3.0 V I/O: 70 ns initial access. - Asymmetrical blocking structure.

- Flash Performance - 16-KWord parameter blocks (Top or - Code Segment at 1.8 V I/O: 85 ns initial Bottom); 64-K Word main blocks. access; 25 ns async page read; 14 ns - Zero-latency block locking. sync reads (tCHQV); 54 MHz CLK. - Absolute write protection with block - Data Segment at 1.8 V I/O: 170 ns initial lock down using F-WP#. access; 55 ns async page read. Device Voltage

- Flash Architecture - Core: VCC = 1.8 V (typ). - Hardware Read-While-Write/Erase. - I/O: VCCQ = 1.8 V or 3.0 V (typ). - 8-Mbit or 16-Mbit Multi-Partition. Device Concurrent Operations (3 Dies) - 2-Kbit One-Time Programmable (OTP) - Buffered EFP: 600 KB per second. Protection Register. - Erase Performance: 384 KB per second - Software Read-While-Write/Erase. (main blocks). - Single Full-Die Partition size. Device Packaging

- Flash Software - 88 balls (8 x 10 active ball matrix). - Intel£ FDI, Intel£ PSM, and Intel£ - Area: 8 x 10 mm or 8 x 11 mm. VFM. - Height: 1.0 mm to 1.4 mm. - Common Flash Interface (CFI). Quality and Reliability - Basic/Extended Command Set. - Extended Temp: -25 °C to +85 °C. - Minimum 100 K flash block erase cycle. DataShee The Intel StrataFlash® Wireless Memory System (LV18/LV30 SCSP); 768-Mbit LVQ Family with Asynchronous Static RAM device offers a high performance code and large embedded data segment plus RAM combination in a co