HCS20MS Overview

Description

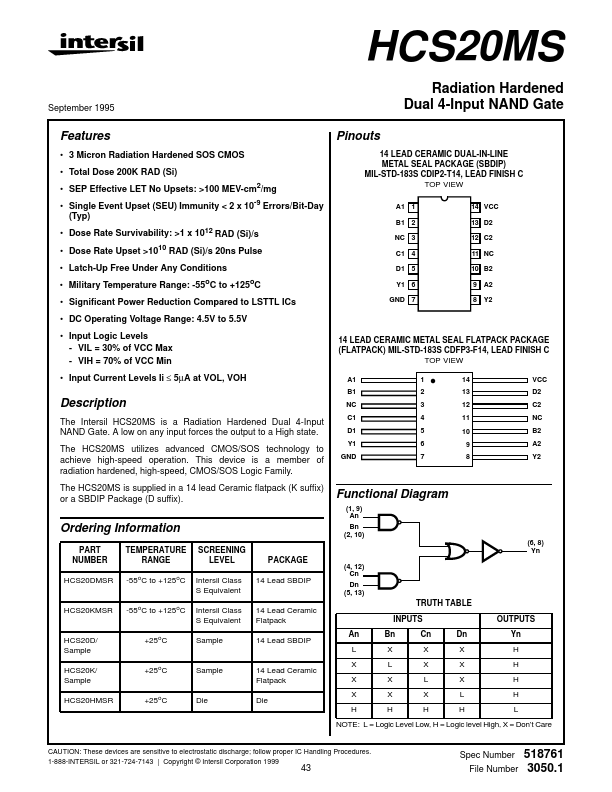

The Intersil HCS20MS is a Radiation Hardened Dual 4-Input NAND Gate. A low on any input forces the output to a High state.

Key Features

- 3 Micron Radiation Hardened SOS CMOS

- Total Dose 200K RAD (Si)

- SEP Effective LET No Upsets: >100 MEV-cm2/mg

- Single Event Upset (SEU) Immunity < 2 x 10-9 Errors/Bit-Day (Typ)

- Dose Rate Survivability: >1 x 1012 RAD (Si)/s