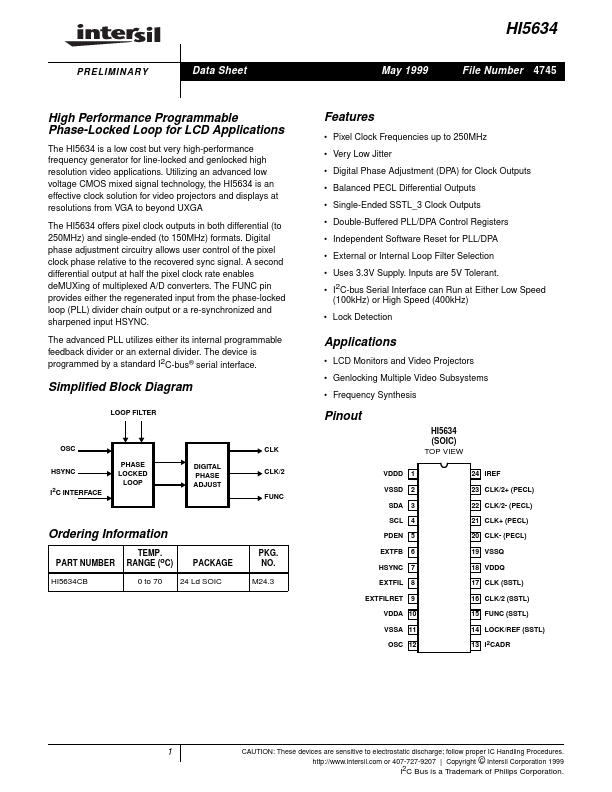

HI5634 Key Features

- Pixel Clock Frequencies up to 250MHz

- Very Low Jitter

- Digital Phase Adjustment (DPA) for Clock Outputs

- Balanced PECL Differential Outputs

- Single-Ended SSTL_3 Clock Outputs

- Double-Buffered PLL/DPA Control Registers

- Independent Software Reset for PLL/DPA

- External or Internal Loop Filter Selection

- Uses 3.3V Supply. Inputs are 5V Tolerant

- I2C-bus Serial Interface can Run at Either Low Speed (100kHz) or High Speed (400kHz)