MWS5101 Overview

Key Specifications

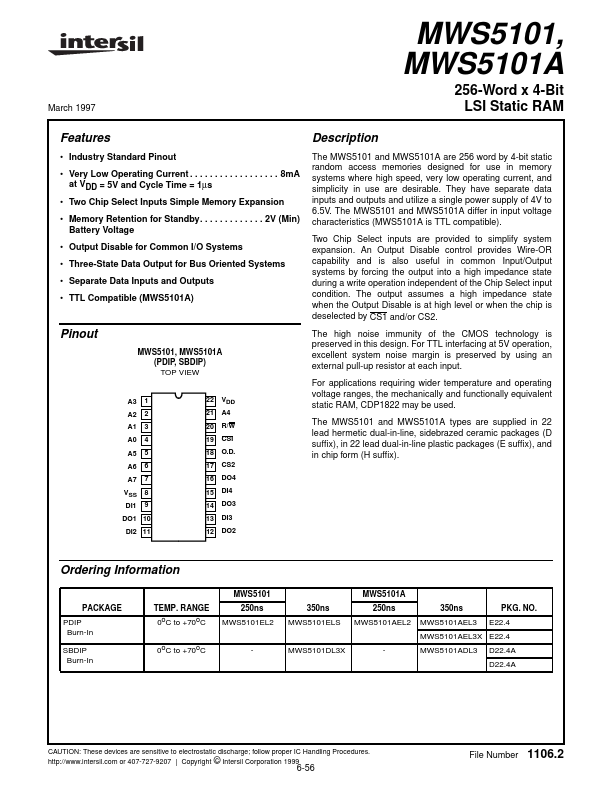

Package: DIP

Operating Voltage: 5 V

Max Voltage (typical range): 6.5 V

Min Voltage (typical range): 4 V

Description

The MWS5101 and MWS5101A are 256 word by 4-bit static random access memories designed for use in memory systems where high speed, very low operating current, and simplicity in use are desirable. They have separate data inputs and outputs and utilize a single power supply of 4V to 6.5V.

Key Features

- Industry Standard Pinout

- Very Low Operating Current . . . . . . . . . . . . . . . . . . 8mA at VDD = 5V and Cycle Time = 1µs

- Two Chip Select Inputs Simple Memory Expansion

- Memory Retention for Standby. . . . . . . . . . . . . 2V (Min) Battery Voltage

- Output Disable for Common I/O Systems