ISPXPLD5000MX Description

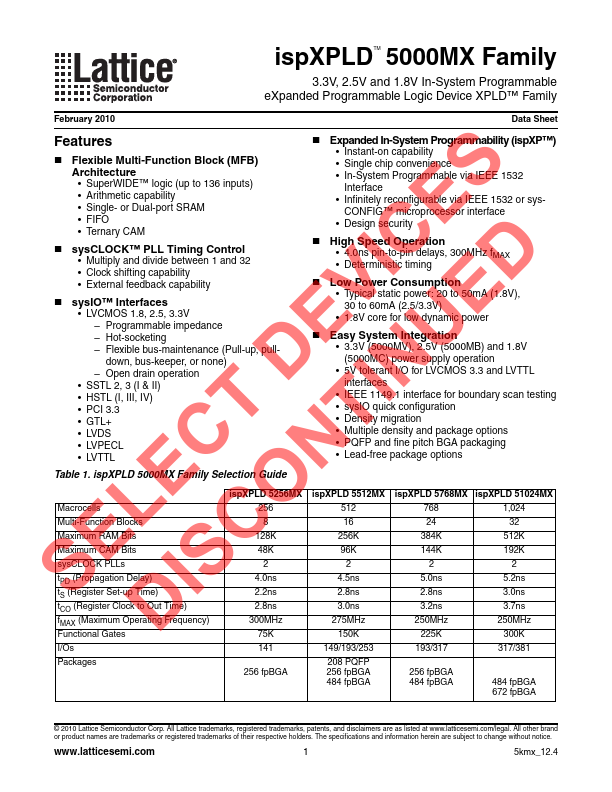

DISSECLOENCTTINDUEEVIDCES ispXPLDTM 5000MX Family 3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD™ Family February 2010 Data Sheet.

ISPXPLD5000MX Key Features

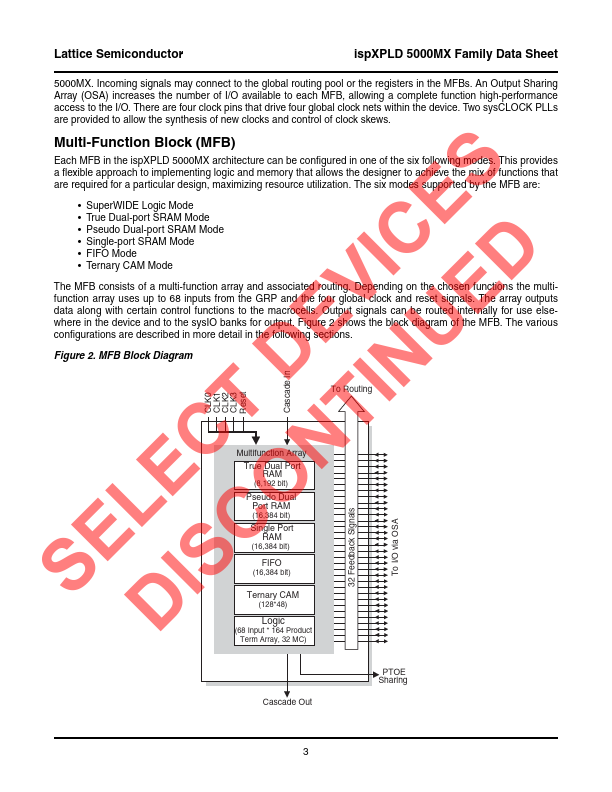

- Flexible Multi-Function Block (MFB) Architecture

- SuperWIDE™ logic (up to 136 inputs)

- Arithmetic capability

- Single- or Dual-port SRAM

- Ternary CAM

- sysCLOCK™ PLL Timing Control

- Multiply and divide between 1 and 32

- Clock shifting capability

- External feedback capability

- sysIO™ Interfaces