DS34S104

DS34S104 is Single/Dual/Quad/Octal TDM-over-Packet Chip manufactured by Maxim Integrated.

- Part of the DS34S101 comparator family.

- Part of the DS34S101 comparator family.

ABRIDGED DATA SHEET

..

Rev: 101708

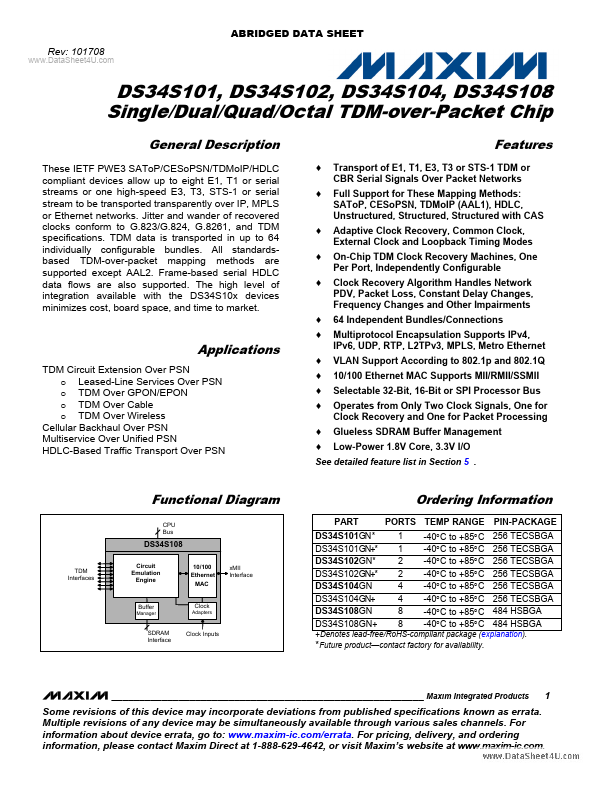

DS34S101, DS34S102, DS34S104, DS34S108 Single/Dual/Quad/Octal TDM-over-Packet Chip

General Description

These IETF PWE3 SATo P/CESo PSN/TDMo IP/HDLC pliant devices allow up to eight E1, T1 or serial streams or one high-speed E3, T3, STS-1 or serial stream to be transported transparently over IP, MPLS or Ethernet networks. Jitter and wander of recovered clocks conform to G.823/G.824, G.8261, and TDM specifications. TDM data is transported in up to 64 individually configurable bundles. All standardsbased TDM-over-packet mapping methods are supported except AAL2. Frame-based serial HDLC data flows are also supported. The high level of integration available with the DS34S10x devices minimizes cost, board space, and time to market.

- -

- -

- -

Features

Transport of E1, T1, E3, T3 or STS-1 TDM or CBR Serial Signals Over Packet Networks Full Support for These Mapping Methods: SATo P, CESo PSN, TDMo IP (AAL1), HDLC, Unstructured, Structured, Structured with CAS Adaptive Clock Recovery, mon Clock, External Clock and Loopback Timing Modes On-Chip TDM Clock Recovery Machines, One Per Port, Independently Configurable Clock Recovery Algorithm Handles Network PDV, Packet Loss, Constant Delay Changes, Frequency Changes and Other Impairments 64 Independent Bundles/Connections Multiprotocol Encapsulation Supports IPv4, IPv6, UDP, RTP, L2TPv3, MPLS, Metro Ethernet VLAN Support According to 802.1p and 802.1Q 10/100 Ethernet MAC Supports MII/RMII/SSMII Selectable 32-Bit, 16-Bit or SPI Processor Bus Operates from Only Two Clock Signals, One for Clock Recovery and One for Packet Processing Glueless SDRAM Buffer Management Low-Power 1.8V Core, 3.3V I/O

Applications

TDM Circuit Extension Over PSN o Leased-Line Services Over PSN o TDM Over GPON/EPON o TDM Over Cable o TDM Over Wireless Cellular Backhaul Over PSN Multiservice Over Unified PSN HDLC-Based Traffic Transport Over PSN

- -

- -

- -

- See detailed feature list in Section 5...