MAX3624A

MAX3624A is Precision Clock Generator manufactured by Maxim Integrated.

19-5005; Rev 0; 10/09

KIT ATION EVALU E L B A IL AVA

..

Low-Jitter, Precision Clock Generator with Four Outputs

General Description Features

- Crystal Oscillator Interface: 19.375MHz to 27MHz

- CMOS Input: 19MHz to 40.5MHz

- Output Frequencies Ethernet: 62.5MHz, 125MHz, 156.25MHz, 312.5MHz Fibre Channel: 106.25MHz, 159.375MHz, 212.5MHz, 318.5MHz SONET/SDH: 77.76MHz, 155.52MHz, 311.04MHz

- Low Jitter 0.14ps RMS (1.875MHz to 20MHz) 0.36ps RMS (12k Hz to 20MHz)

- Excellent Power-Supply Noise Rejection

- No External Loop Filter Capacitor Required

The MAX3624A is a low-jitter, precision clock generator optimized for networking applications. The device integrates a crystal oscillator and a phase-locked loop (PLL) clock multiplier to generate high-frequency clock outputs for Ethernet, Fibre Channel, SONET/SDH, and other networking applications. Maxim’s proprietary PLL design Features ultra-low jitter (0.36ps RMS) and excellent power-supply noise rejection, minimizing design risk for network equipment. The MAX3624A has three LVPECL outputs and one LVCMOS output. Selectable output dividers and a selectable feedback divider allow a range of output frequencies.

Applications

Ethernet Networking Equipment Fibre Channel Storage Area Network SONET/SDH Network

Pin Configuration and Typical Application Circuit appear at end of data sheet.

Ordering Information

PART MAX3624AETJ+ TEMP RANGE -40°C to +85°C PIN-PACKAGE 32 TQFN-EP-

+Denotes a lead(Pb)-free/Ro HS-pliant package.

- EP = Exposed pad.

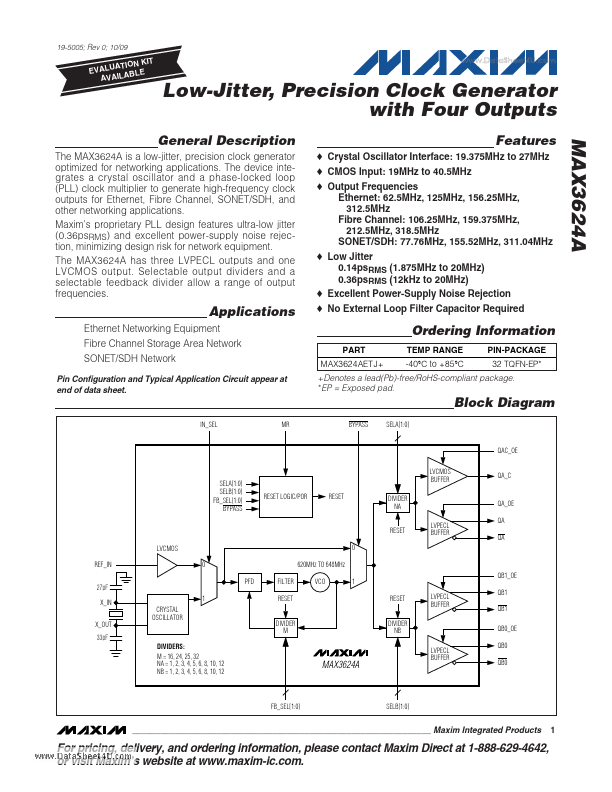

Block Diagram

IN_SEL MR BYPASS SELA[1:0]

QAC_OE LVCMOS BUFFER RESET LOGIC/POR RESET DIVIDER NA LVPECL BUFFER

QA_C

SELA[1:0] SELB[1:0] FB_SEL[1:0] BYPASS

QA_OE QA QA

RESET LVCMOS REF_IN 27p F X_IN CRYSTAL OSCILLATOR X_OUT 33p F DIVIDERS: M = 16, 24, 25, 32 NA = 1, 2, 3, 4, 5, 6, 8, 10, 12 NB = 1, 2, 3, 4, 5, 6, 8, 10, 12 DIVIDER M DIVIDER NB 1 0 PFD FILTER RESET 620MHz TO 648MHz VCO 1 RESET 0

QB1_OE LVPECL BUFFER QB1 QB1 QB0_OE LVPECL BUFFER QB0...