MAX9426

Description

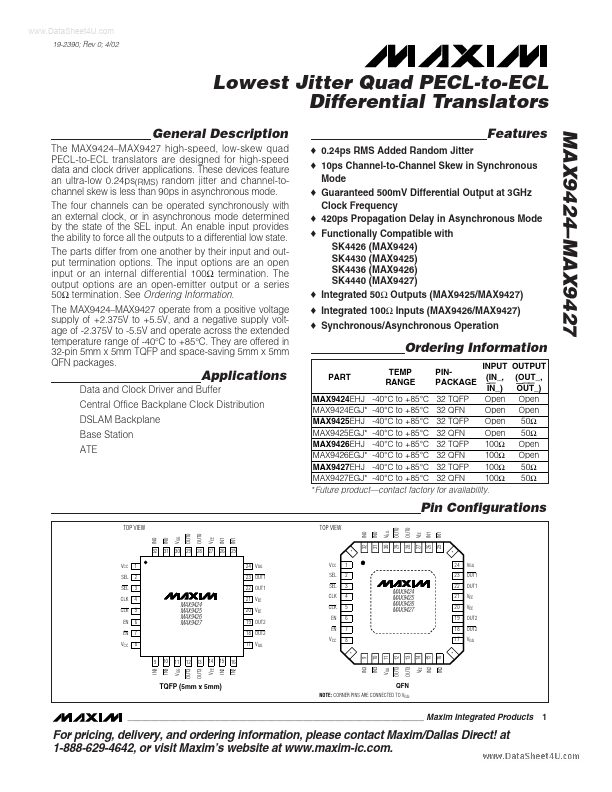

The MAX9424- MAX9427 high-speed, low-skew quad PECL-to-ECL translators are designed for high-speed data and clock driver applications. These devices feature an ultra-low 0.24ps(RMS) random jitter and channel-tochannel skew is less than 90ps in asynchronous mode. The four channels can be operated synchronously with an external clock, or in asynchronous mode determined by the state of the SEL input. An enable input provides the ability to force all the outputs to a differential low state. The parts differ from one another by their input and output termination options. The input options are an open input or an internal differential 100Ω termination. The output options are an open-emitter output or a series 50Ω termination. See Ordering Information. The MAX9424- MAX9427 operate from a positive voltage supply of +2.375V to +5.5V, and a negative supply voltage of -2.375V to -5.5V and operate across the extended temperature range of -40°C to +85°C. They are offered in 32-pin 5mm x...