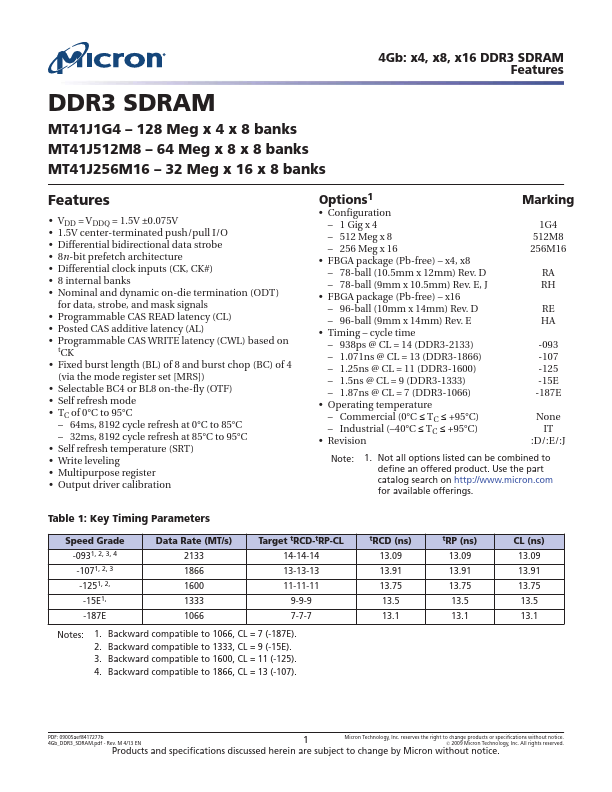

MT41J1G4

Key Features

- VDD = V DDQ = 1.5V ±0.075V 1.5V center-terminated push/pull I/O Differential bidirectional data strobe 8n-bit prefetch architecture Differential clock inputs (CK, CK#) 8 internal banks Nominal and dynamic on-die termination (ODT) for data, strobe, and mask signals Programmable CAS READ latency (CL) Posted CAS additive latency (AL) Programmable CAS WRITE latency (CWL) based on tCK Fixed burst length (BL) of 8 and burst chop (BC) of 4 (via the mode register set [MRS]) Selectable BC4 or BL8 on-the-fly (OTF) Self refresh mode TC of 0°C to 95°C - 64ms, 8192 cycle refresh at 0°C to 85°C - 32ms, 8192 cycle refresh at 85°C to 95°C Self refresh temperature (SRT) Write leveling Multipurpose register Output driver calibration Options1

- Configuration - 1 Gig x 4 - 512 Meg x 8 - 256 Meg x 16

- FBGA package (Pb-free) - x4, x8 - 78-ball (10.5mm x 12mm) Rev. D - 78-ball (9mm x 10.5mm) Rev. E, J

- FBGA package (Pb-free) - x16 - 96-ball (10mm x 14mm) Rev. D - 96-ball (9mm x 14mm) Rev. E

- Timing - cycle time - 938ps @ CL = 14 (DDR3-2133) - 1.071ns @ CL = 13 (DDR3-1866) - 1.25ns @ CL = 11 (DDR3-1600) - 1.5ns @ CL = 9 (DDR3-1333) - 1.87ns @ CL = 7 (DDR3-1066)

- Operating temperature - Commercial (0°C ≤ T C ≤ +95°C) - Industrial (-40°C ≤ T C ≤ +95°C)

- Revision Note: Marking