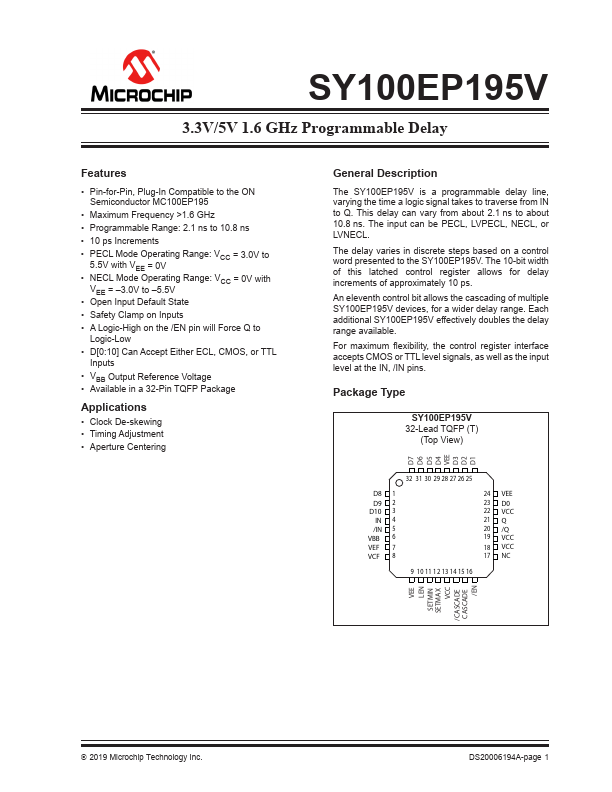

SY100EP195V Key Features

- Pin-for-Pin, Plug-In patible to the ON Semiconductor MC100EP195

- Maximum Frequency >1.6 GHz

- Programmable Range: 2.1 ns to 10.8 ns

- 10 ps Increments

- Open Input Default State

- Safety Clamp on Inputs

- D[0:10] Can Accept Either ECL, CMOS, or TTL

- VBB Output Reference Voltage

- Available in a 32-Pin TQFP Package