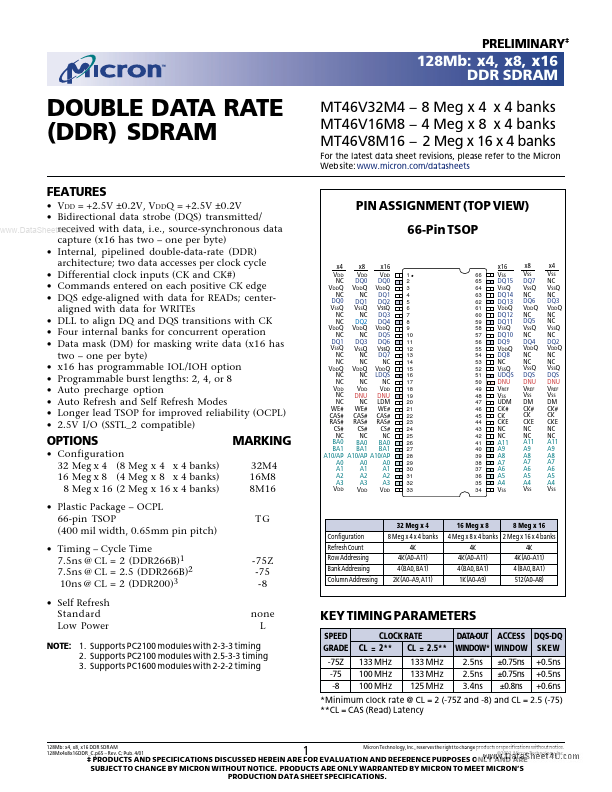

46V16M8 Overview

Key Specifications

Package: TSSOP

Mount Type: Surface Mount

Pins: 66

Operating Voltage: 2.5 V

Key Features

- VDD = +2.5V ±0.2V, VDDQ = +2.5V ±0.2V

- Bidirectional data strobe (DQS) transmitted/ received with data, i.e., source-synchronous data capture (x16 has two – one per byte)

- Internal, pipelined double-data-rate (DDR) architecture; two data accesses per clock cycle

- Differential clock inputs (CK and CK#)

- Commands entered on each positive CK edge