MT9LSDT872

MT9LSDT872 is SYNCHRONOUS DRAM MODULE manufactured by Micron Technology.

- Part of the MT9LSDT1672 comparator family.

- Part of the MT9LSDT1672 comparator family.

FEATURES

- JEDEC-standard 168-pin, dual in-line memory module (DIMM)

- PC133- and PC100-pliant

- Registered inputs with one-clock delay

- Phase-lock loop (PLL) clock driver to reduce loading

- Utilizes 133 MHz and 125 MHz SDRAM ponents

- ECC-optimized pinout

- 64MB (8 Meg x 72) and 128MB (16 Meg x 72)

- Single +3.3V ±0.3V power supply

- Fully synchronous; all signals registered on positive edge of PLL clock

- Internal pipelined operation; column address can be changed every clock cycle

- Internal SDRAM banks for hiding row access/ precharge

- Programmable burst lengths: 1, 2, 4, 8, or full page

- Auto Precharge and Auto Refresh Modes

- Self Refresh Mode

- 64ms, 4,096-cycle refresh

- LVTTL-patible inputs and outputs

- Serial Presence-Detect (SPD)

MT9LSDT872, MT9LSDT1672

For the latest data sheet, please refer to the Micron Web site: .micronsemi./datasheets/datasheet.html

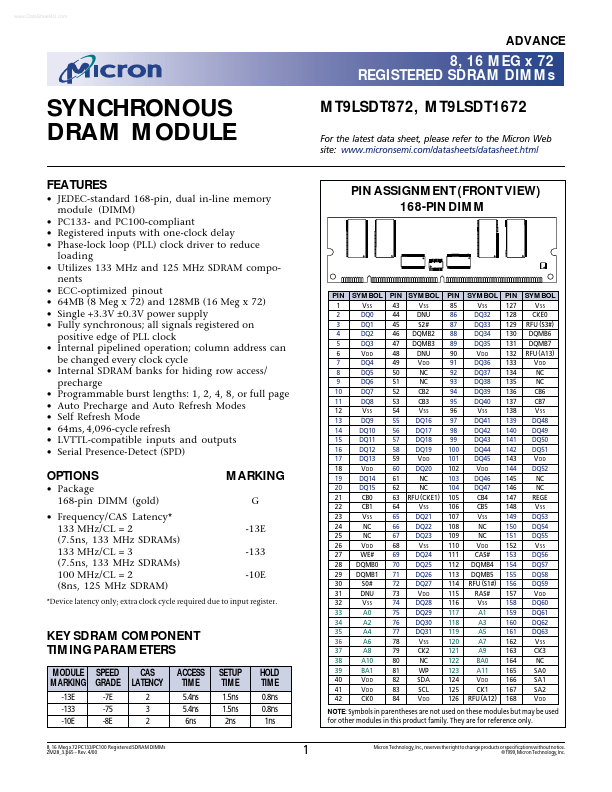

PIN ASSIGNMENT (FRONT VIEW) 168-PIN DIMM

OPTIONS

- Package 168-pin DIMM (gold)

- Frequency/CAS Latency- 133 MHz/CL = 2 (7.5ns, 133 MHz SDRAMs) 133 MHz/CL = 3 (7.5ns, 133 MHz SDRAMs) 100 MHz/CL = 2 (8ns, 125 MHz SDRAM)

MARKING

G -13E -133 -10E

- Device latency only; extra clock cycle required due to input register.

KEY SDRAM PONENT TIMING PARAMETERS

MODULE MARKING -13E -133 -10E SPEED GRADE -7E -75 -8E CAS LATENCY 2 3 2 ACCESS TIME 5.4ns 5.4ns 6ns SETUP TIME 1.5ns 1.5ns 2ns HOLD TIME 0.8ns 0.8ns 1ns

PIN 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42

SYMBOL V SS DQ0 DQ1 DQ2 DQ3 V DD DQ4 DQ5 DQ6 DQ7 DQ8 V SS DQ9 DQ10 DQ11 DQ12 DQ13 V DD DQ14 DQ15 CB0 CB1 V SS NC NC V DD WE# DQMB0 DQMB1 S0# DNU V SS A0 A2 A4 A6 A8 A10 BA1 V DD V DD CK0

PIN SYMBOL 43 V SS 44 DNU 45 S2# 46 DQMB2 47 DQMB3 48 DNU 49 V DD 50 NC 51 NC 52 CB2 53 CB3 54 V SS 55 DQ16 56 DQ17 57 DQ18 58 DQ19 59 V DD 60 DQ20 61 NC 62 NC 63 RFU (CKE1) 64 V SS 65 DQ21 66 DQ22 67 DQ23 68 V SS 69 DQ24 70 DQ25 71 DQ26 72 DQ27 73 V DD 74 DQ28 75 DQ29 76 DQ30 77 DQ31 78 V SS 79...