HSMBJSAC36 Description

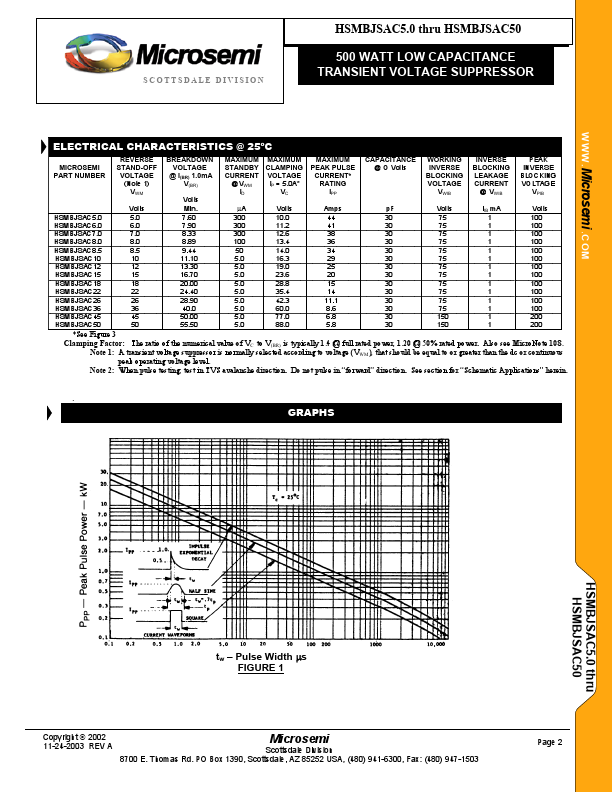

The HSMBJSAC transient voltage suppressor (TVS) series rated at 500 Watts provides an added rectifier element as shown in Figure 4 to achieve low capacitance in applications for data or signal lines. The low capacitance rating of less than 30 pF may be used for protecting higher frequency applications in inductive switching environments or electrical systems involving secondary lightning effects per IEC61000-4-5 as...

HSMBJSAC36 Applications

- Unidirectional low-capacitance TVS series (for bidirectional see Figure 6)

- Suppresses transient up to 500 Watts Peak Pulse Power @ 10/1000 µs

- Improved performance in low capacitance of 30 pF