ZL40241

Key Features

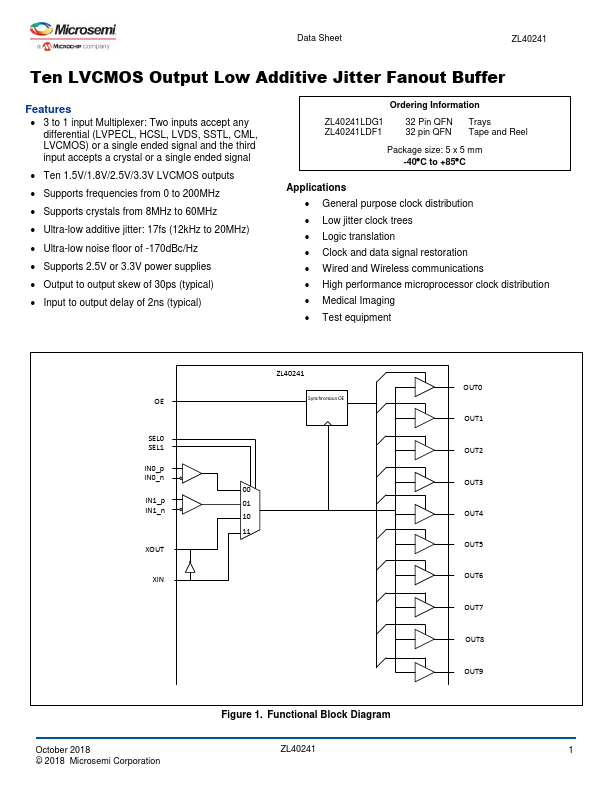

- 3 to 1 input Multiplexer: Two inputs accept any differential (LVPECL, HCSL, LVDS, SSTL, CML, LVCMOS) or a single ended signal and the third input accepts a crystal or a single ended signal

- Ten 1.5V/1.8V/2.5V/3.3V LVCMOS outputs

- Supports frequencies from 0 to 200MHz

- Supports crystals from 8MHz to 60MHz

- Ultra-low additive jitter: 17fs (12kHz to 20MHz)

- Ultra-low noise floor of -170dBc/Hz

- Supports 2.5V or 3.3V power supplies

- Output to output skew of 30ps (typical)

- Input to output delay of 2ns (typical)