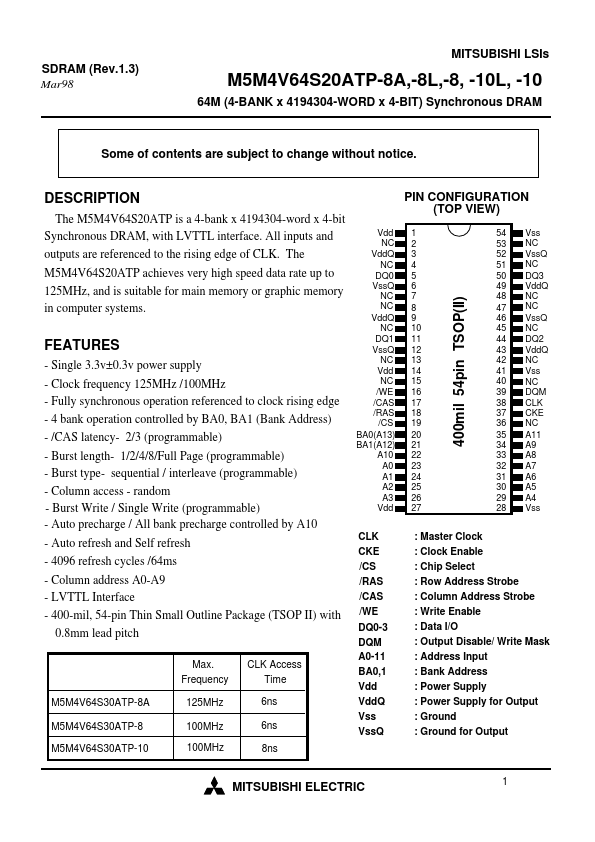

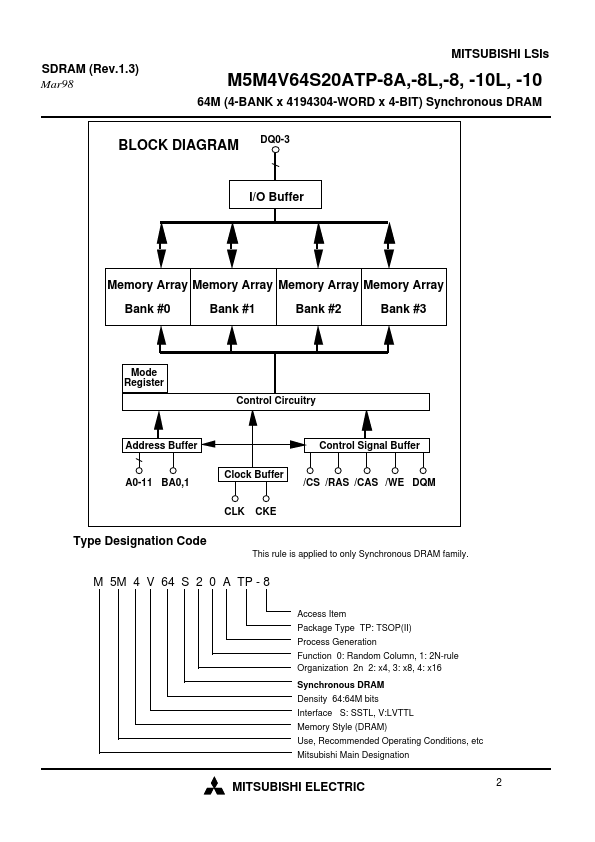

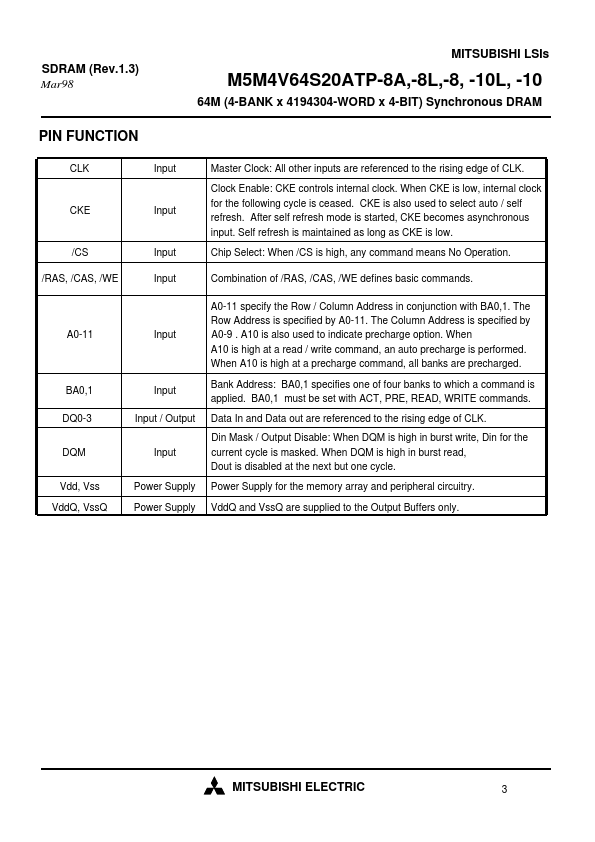

M5M4V64S20ATP-8

64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM (Mitsubishi)

M5M4V64S20ATP-8A

64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM (Mitsubishi)

M5M4V64S20ATP-10

64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM (Mitsubishi)

M5M4V64S20ATP-10L

64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM (Mitsubishi)

M5M4V64S20ATP-12

64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM (Mitsubishi)

M5M4V64S30ATP-10

64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM (Mitsubishi)

M5M4V64S30ATP-10L

64M (4-BANK x 2097152-WORD x 8-BIT) Synchronous DRAM (Mitsubishi)

M5M4V64S30ATP-12

64M (4-BANK x 2097152-WORD x 8-BIT) Synchronous DRAM (Mitsubishi)