V54C3256804VT Overview

Description

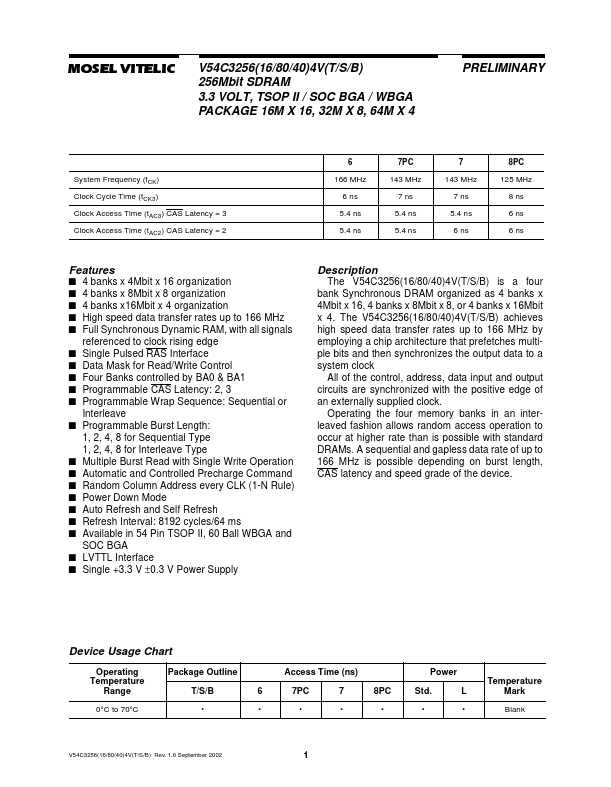

The V54C3256(16/80/40)4V(T/S/B) is a four bank Synchronous DRAM organized as 4 banks x 4Mbit x 16, 4 banks x 8Mbit x 8, or 4 banks x 16Mbit x 4. The V54C3256(16/80/40)4V(T/S/B) achieves high speed data transfer rates up to 166 MHz by employing a chip architecture that prefetches multiple bits and then synchronizes the output data to a system clock All of the control, address, data input and output circuits are synchronized with the positive edge of an externally supplied clock.