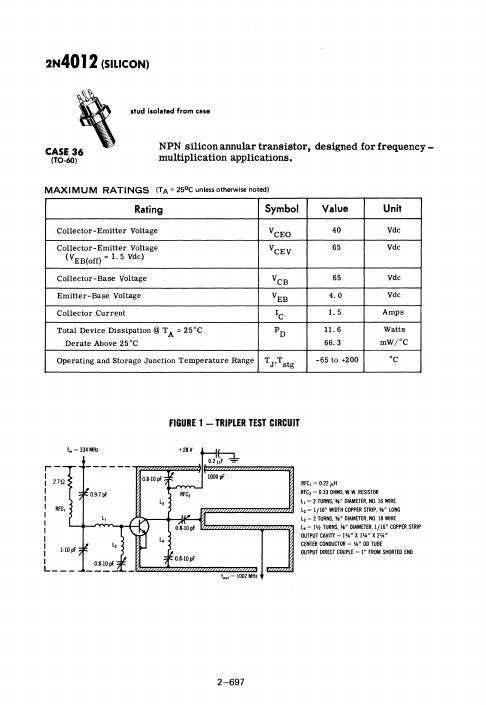

| Part | 2N4012 |

|---|---|

| Description | NPN silicon annular transistor |

| Category | Transistor |

| Manufacturer | Motorola Semiconductor |

| Size | 97.13 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 2N4014 | Central Semiconductor | SILICON NPN TRANSISTOR |

| 2N4014 | STMicroelectronics | Silicon Planar Epitaxial transistor |

| 2N4013 | Motorola Semiconductor | Transistors |

| 2N4014 | Motorola Semiconductor | Transistors |

| 2N4007 | Crystalonics | Silicon Epitaxial Junction PNP Switching Transistor |