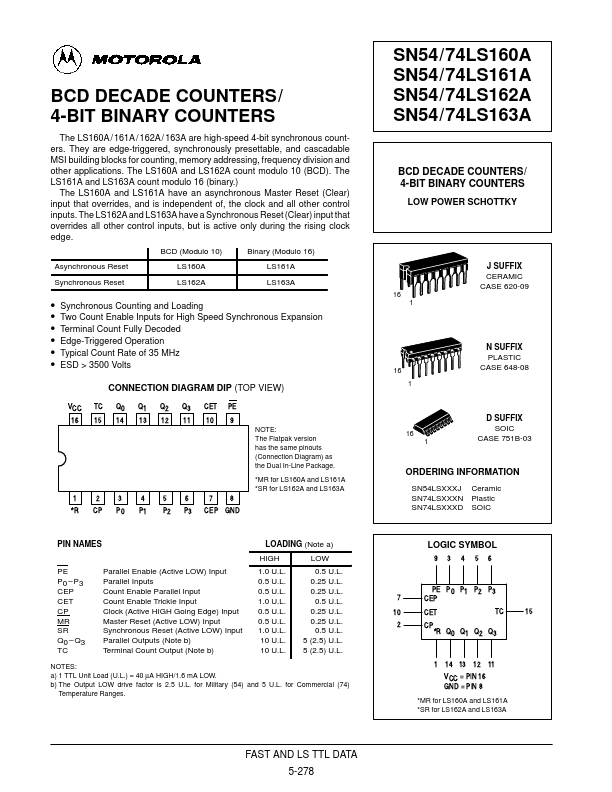

| Part | 54LS161A |

|---|---|

| Description | BCD DECADE COUNTERS / 4-BIT BINARY COUNTERS |

| Manufacturer | Motorola Semiconductor |

| Size | 157.30 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| 74LS168 | National Semiconductor | 54LS168 Synchronous Bi-Directional BCD Decade Counter |

| 54LS164 | National Semiconductor | 8-Bit Parallel-Out Serial Shift Registers |

| 54LS164 | Raytheon | 8-Bit Parallel-Out Serial Shift Registers |

| 54LS164 | Texas Instruments | 8-Bit Parallel-Out Shift Register Register |

| 54LS169 | National Semiconductor | Synchronous 4-Bit Up/Down Binary Counter |