|

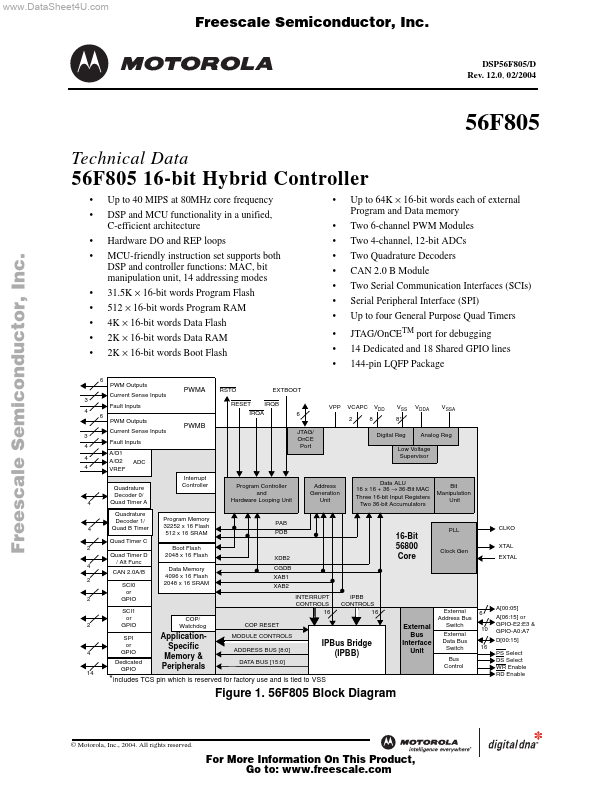

56F805

|

Freescale Semiconductor |

16-bit Digital Signal Controllers |

|

56F800

|

Freescale Semiconductor |

16-bit Digital Signal Controllers |

|

56F803

|

Freescale Semiconductor |

16-bit Digital Signal Controllers |

|

56F8023

|

Freescale Semiconductor |

16-bit Digital Signal Controllers |

|

56F801

|

Freescale Semiconductor |

16-bit Digital Signal Controllers |

|

56F8013

|

Freescale Semiconductor |

16-bit Digital Signal Controllers |

|

56F8014

|

Freescale Semiconductor |

16-bit Digital Signal Controllers |

|

56F802

|

Freescale Semiconductor |

16-bit Digital Signal Controllers |

|

56F8025

|

Freescale Semiconductor |

Digital Signal Controller Product Brief |

|

56F8036

|

Freescale Semiconductor |

16-bit Digital Signal Controllers |