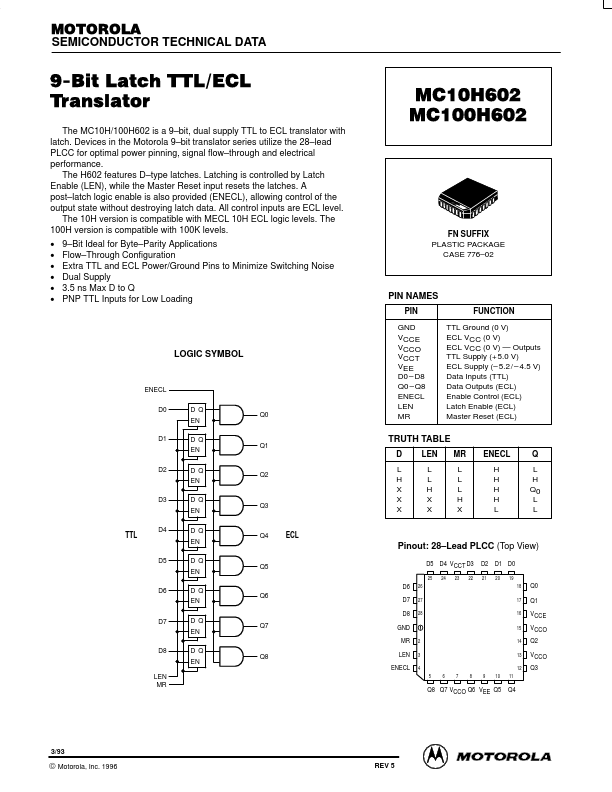

| Part | MC100H602 |

|---|---|

| Description | 9-Bit Latch TTL/ECL Translator |

| Manufacturer | Motorola Semiconductor |

| Size | 83.96 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| MC100H602 | onsemi | 9-Bit Latch TTL/ECL Translator |

| MC100H604 | onsemi | Registered Hex TTL/ECL Translator |

| MC100H605 | onsemi | Registered Hex ECL/TTL Translator |

| MC100H600 | onsemi | 9-Bit TTL/ECL Translator |

| MC100H601 | onsemi | 9-Bit ECL/TTL Translator |