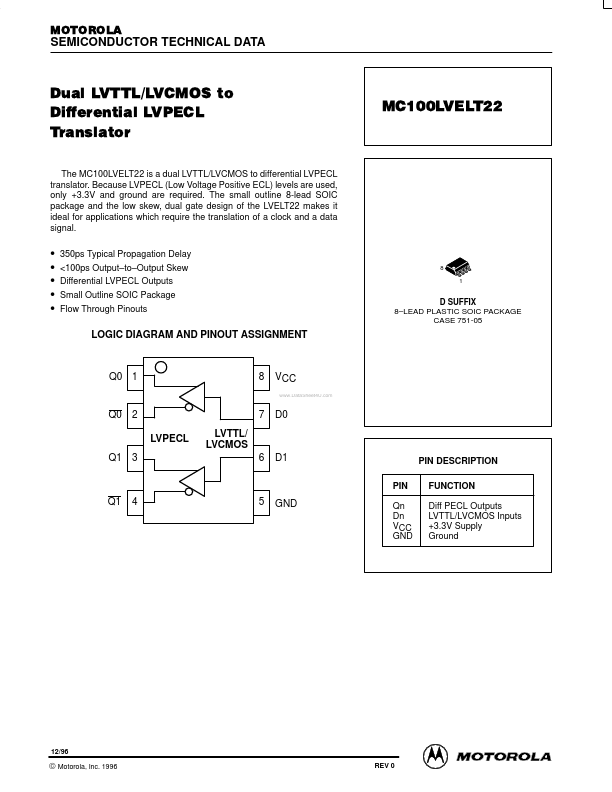

MC100LVELT22 Overview

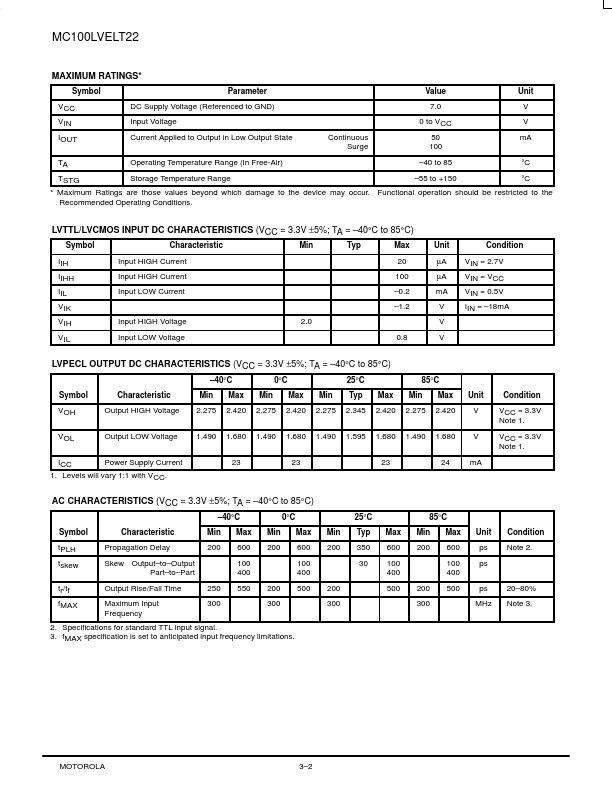

FUNCTION Diff PECL Outputs LVTTL/LVCMOS Inputs +3.3V Supply Ground Q1 4 5 GND Qn Dn VCC GND 12/96 © Motorola, Inc. Functional operation should be restricted to the Remended Operating Conditions. LVTTL/LVCMOS INPUT DC CHARACTERISTICS (VCC = 3.3V ±5%;.