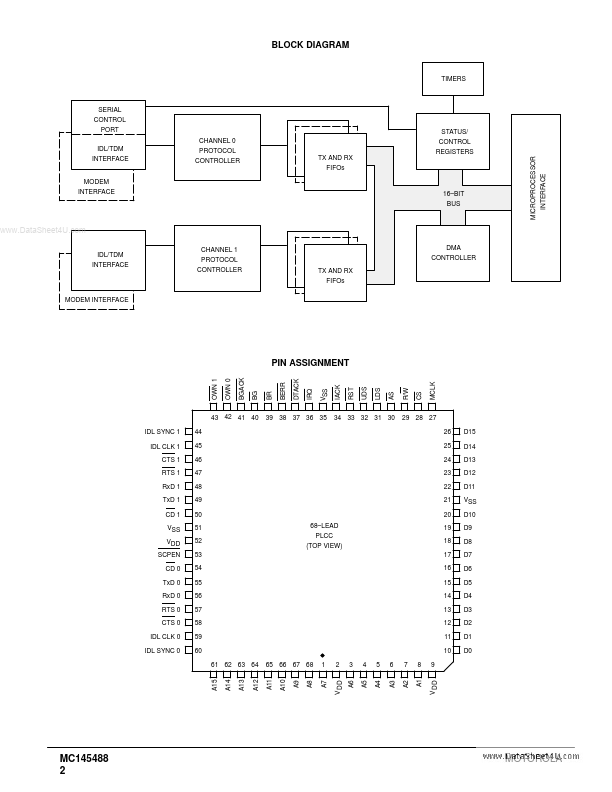

MC145488 Key Features

- Two Independent Full-Duplex Bit-Oriented Protocol Controllers Support HDLC, SDLC, CCITT X.25, CCITT Q.921 (LAPD), and V.

- Four-Channel On-Chip DMA Controller

- 64 kbyte Address Range with Expansion Control

- Internal Programmable Wait-State Generator

- Two Buffer Descriptors for Each Receiver Channel

- patible with 68000 and 80186 Bus Structures

- Non-Multiplexed 16- or 8-Bit Data Bus

- Frame Sizes up to 4096 bytes

- Bit-Level HDLC Processing Including

- Flag Generation/Detection