Datasheet Summary

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Order this document by MPC2002/D

256KB and 512KB BurstRAM™ Secondary Cache Module for PowerPC™

- Based Systems

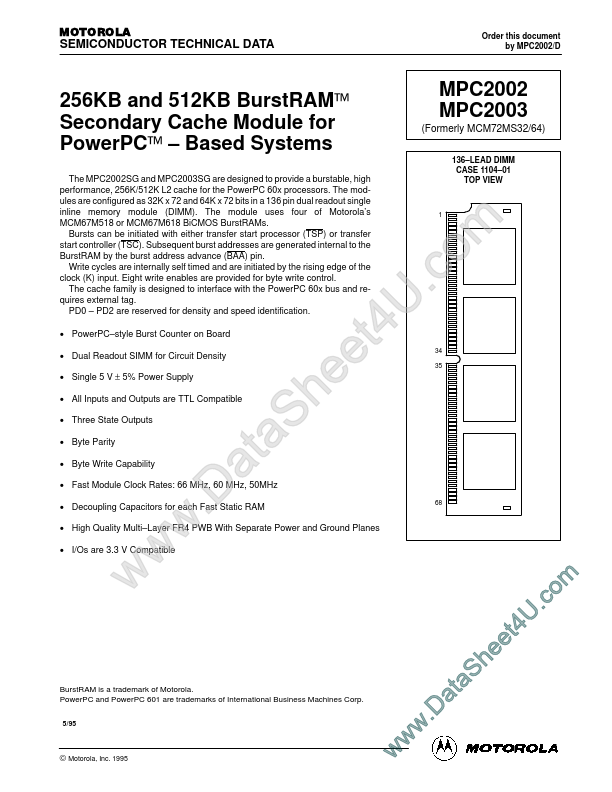

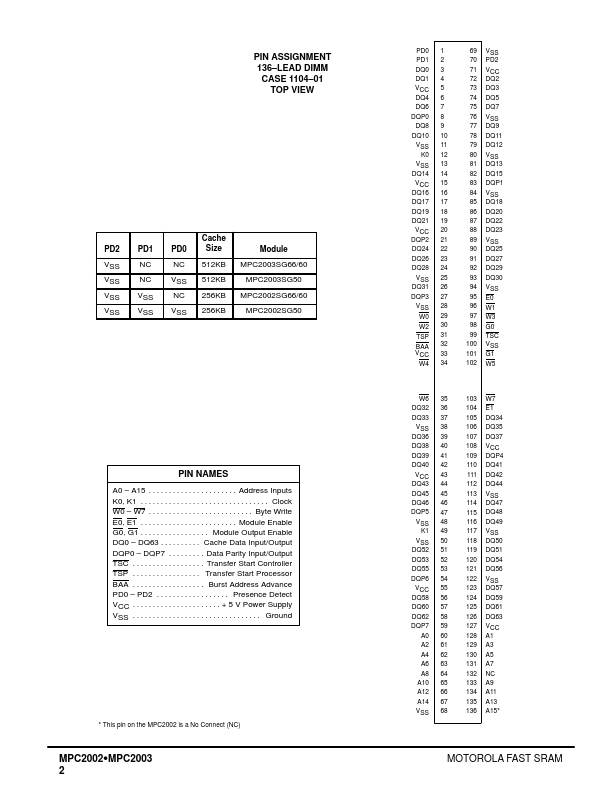

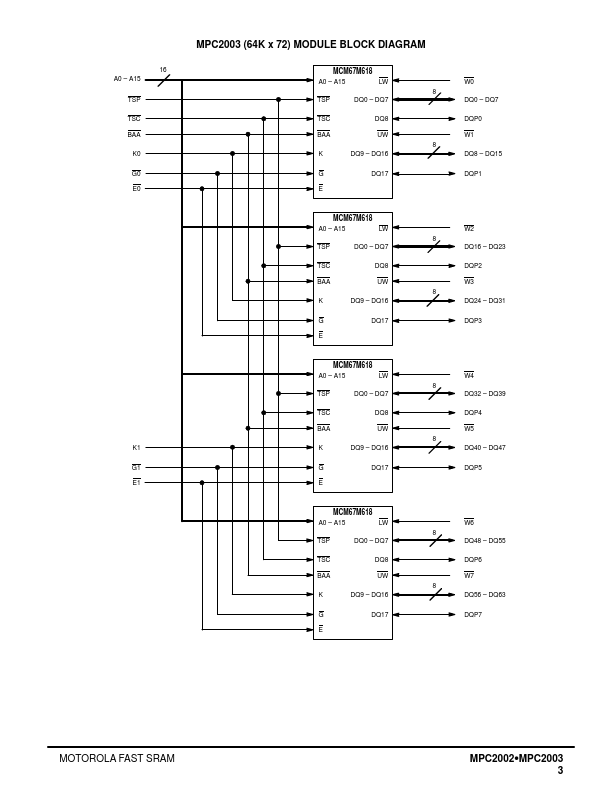

The MPC2002SG and MPC2003SG are designed to provide a burstable, high performance, 256K/512K L2 cache for the PowerPC 60x processors. The modules are configured as 32K x 72 and 64K x 72 bits in a 136 pin dual readout single inline memory module (DIMM). The module uses four of Motorola’s MCM67M518 or MCM67M618 BiCMOS BurstRAMs. Bursts can be initiated with either transfer start processor (TSP) or transfer start controller (TSC). Subsequent burst addresses are generated internal to the BurstRAM by the burst address advance (BAA) pin. Write...