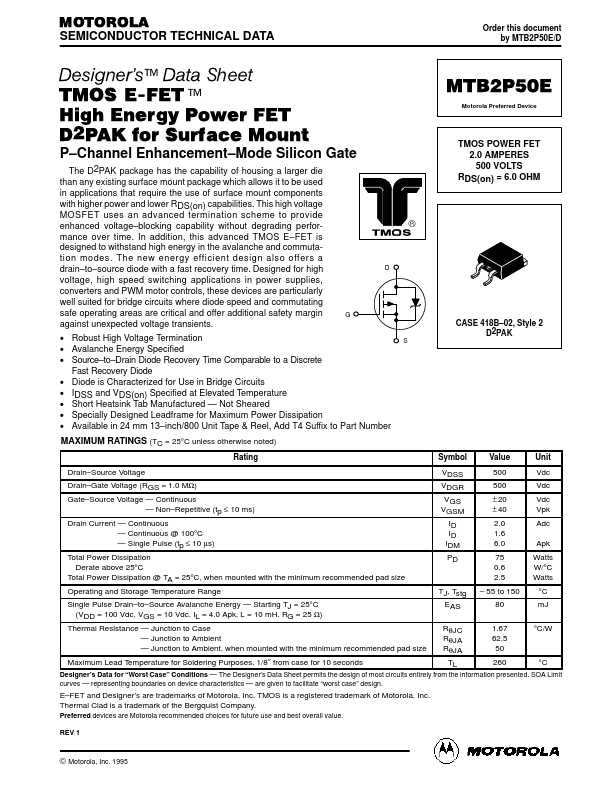

| Part | MTB2P50E |

|---|---|

| Description | TMOS POWER FET |

| Manufacturer | Motorola Semiconductor |

| Size | 273.90 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| CBT3253 | Nexperia | Dual 1-of-4 FET multiplexer/demultiplexer |

| TL074C | STMicroelectronics | LOW NOISE J-FET QUAD OPERATIONAL AMPLIFIER |

| CBT3125 | Nexperia | Quadruple FET bus switch |